# MODELING of dislocation evolution in Multi-junction based Photovoltaic devices

Tarek M. Hatem and Mohamed T. Elewa

**Abstract**—Genuine Processing techniques have been developed to minimize density of dislocations and other defects originating from thermal stresses present in Multi Junction PVs. Embedded Void Approach; (EVA) was used to address the defects evolution in GaAs growth on Si substrates. In attempts to study void effect on dislocation generation; elastic models were prepared for voided and un-voided structures. Stresses and displacements were compared and related to alteration in dislocation density.

*Keywords*—Dislocation Density, Multi-junction solar cells, Finite Element Modeling, Thermal Stresses

# I. INTRODUCTION

THE achievement of a PV device that collects photons in 1.4 eV-1.0 eV range requires considerable effort. It happens to be the main obstacle in achieving cascade solar cells with conversion  $\eta > 45\%$ . In attempts to address this dilemma, N was added to GaAs forming GaAsN to reduce Eg to ~1.0 eV while maintaining the lattice matched conditions to GaAs. The result was poor diffusion length, minority carrier lifetime, and low open circuit voltage [1]. Following the early reports, where an inverted structure of InGaP grown on GaAs substrate, lattice constant is graded to grow  $In_{0.3}Ga_{0.7}As$ followed by etching off the GaAs substrate, the problem is in handling ultra-thin film in large scale production [2]. InGaAs/GaAsP strained layered super-lattice (SLS) was lattice matched to GaAs and was reported successful to partially absorb photons in the 1.4 - 1.2 eV range however it required hundreds of SLS periods to fully absorb 1.4 - 1.0 eV, [3]. GaAs growth on Si substrates seem to offer the solution for the 1.0 eV sub cell problem, unfortunately GaAs/Si experiences thermal expansion mismatch of 54%, and a lattice mismatch of 4.1% These mismatches initiate dislocations at the interface that run through the crystalline structure of the films and terminate at free surfaces. Dislocations act as scattering centers affecting carriers' lifetime and setting a limit on the performance, reliability, and lifetime of MJ-PV devices. Voids act as a free surface for inhibiting dislocation propagation, this was the main principle of Embedded Void Approach (EVA) [4] where a high density of micro-voids-a

few micrometers in length and less than a micrometer in diameter—are introduced into the GaAs layer near its interface with Si. Experimentally, the three dimensional void network has an average density of about  $10^8 \text{ cm}^{-2}$ , dislocations could be reduced uniformly over large area of substrates, by two orders of magnitude from  $10^9 \text{ cm}^{-2}$  to  $10^7 \text{ cm}^{-2}$ , [5]. Dislocations propagate to voids in their vicinity or can be redirected to be trapped in the three dimensional networks. Voids act as expansion joints for lattice mismatches as well. In this paper, the problem is parsed numerically where defects evolution is simulated during the processing of GaAs/Si device whileaccounting for temperature variations. A static study was performed on two elastic models, to confirm effect of void on defect density.

## II. PROCEDURE

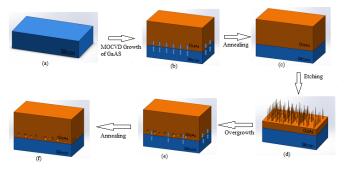

Void generation process is a three-step process that involves growth, etching and regrowth. It begins with growth of GaAs on a Si substrate by Metal-Organic Chemical Vapor Deposition (MOCVD) at temperatures greater than 600°C, this initiates intrinsic stresses, followed by annealing at elevated temperature around 1000°C for stress relaxation. GaAs is then etched, using mask-less inductively coupled plasma- reactive ion etching mask-less (ICP-RIE), to expose different planes of GaAs and generate Nanowires (NWs). These planes have different growth rates of GaAs facets, thus generating voids filled with low-pressure gas  $H_2$ . In the final step, epitaxial GaAs is overgrown on the GaAs NW template and again followed by annealing for stress relaxation.

Numerically, an Elastic continuum Model was built, GaAs/Si device was modeled with dimensions 30 µmx 12.5 µm for width and length, respectively. The Sketch chiefly focused at the interface region where a partition divided the length into two non-equal parts; GaAs has length of 2.5 µm whereas Si length is 10 µm, voids have random size and vertical orientation with average length of 1 micrometer. Material Properties identified for Si and GaAs are listed in table 1. Simulation was run on ABAQUS software. Unit system used was MPA, as classified by ANSYS, which is similar to SI and CGS unit systems, where mass is in tones; length is in mm and pressure in MPa. Young's Modulus and Poisson's Ratio for both materials were considered for (111) plane; closely packed plane. Material Parameters selected are listed in table Iin appendix. Static general analysis was performed where maximum number of increments was 1, minimum increment size of  $1e^{-5}$  and maximum of 1.

Tarek M. Hatemwas with North Carolina State University, Raleigh, NC27695USA. He is now with Mechanical Engineering Department, British University in Egypt, El Sherouk, CA 11837 Egypt.(phone: 202-2689-0000; fax: 202-263-00010; e-mail: tarek.hatem@bue.edu.eg).

Mohamed T Elewais with theMechanical Engineering Department, British University in Egypt, El Sherouk, CA11837Egypt. (e-mail: mohamed.elewa@bue.edu.eg).

Thermal stresses occur when structure temperature drops from 1000°C, annealing temperature to 25°C, room temperature. The model experiences two steps each with the assigned temperature. Displacement Constraints were applied by using boundary conditions to the top right node of the substrate in x and y, since all translational and rotational degrees of freedom need to be constrained, i.e. U1= U2= UR3=0. For inspecting the validity of stress reduction with voids, the previous procedure was carried out for Void and no-Void models. Approximate mesh global seed size of 0.0005. The un-voided model was structure-meshed; voids were free meshed with minimized mesh transition medial axis as complex geometry prevailed. For both models, Element shape was Quadratic and Element type was set to CPS4R, denoting bilinear, plane stress, quadrilateral, reduced 4-node integration. The finite element mesh contained 2171 nodes and 1994 elements for mesh with voids whereas un-voided mesh contained 1586 nodes and 1500 elements. Results based on average element output at nodes, averaging threshold 75%

Figure1EVA Fabrication process chart a) Silicon Substrate b) MOCVD growth c) Annealing d) Etching e) Overgrowth and creating voids f) Annealing

### III. DISCUSSION

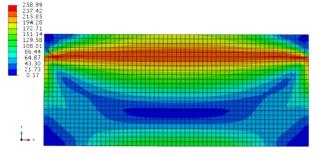

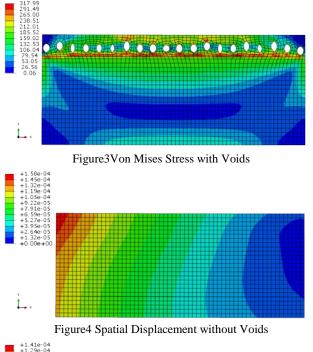

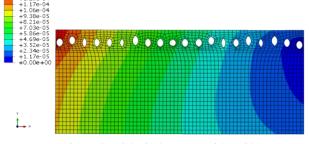

After implementing nearly 20 voids in the voided structure, it should be mentioned that obtained interface stress results, measured from silicon substrate, were reduced from 216 MPa, without voids to 186 MPa with voids. Whereas stresses measured from GaAs are 265 MPawith voids and 216 MPawithout. Stress value at top of GaAs film was higher for voided structure; stresses peaked at the center of film top with186 MPa, without voids stress value is 173 MPa. An explanation for raise in stress is that voids act as discontinuities or stress singularities in the structure levitating stresses while annihilating dislocations. It is the main purpose of EVA to reduce defects number which act as barriers for charge carriers in the semiconductors; voids result in higher fatigue and less defects. Lower surface stresses signify less dislocation densities. Stress Contour plots acquired are shown in fig. 1 and 2 for both models. Substrate bottom stresses were reduced significantly from 108 MPa to 79.5 MPa when voids were applied. Maximum Spatial Displacement, 0.141 µm, occurred at top of film left side, for voided model. Same BCs were applied to un-voided model; the displacement had a higher value of  $0.158 \ \mu m$ . Spatial displacement plots are

shown in fig. 3 and 4. It was perceived that voids closer to the interface, yielded higher stress values, at that region, than those at a greater distance from the interface. Unfortunately, when voids are shifted upwards, they raise stresses at other regions i.e. GaAs film top. Void network positioning is crucial. Moreover, it was noticed that resulting stresses depend on void density; this was confirmed when a stress of 248 MPa at GaAs and 124 MPa at Si layer were obtained after implementing 40 voids.

Assuming an elastic response from, the effect of raising temperature from  $T_0$  to T initiates thermal stress,  $\sigma_T$  which is given by

$$\Delta \sigma_T = E \,\Delta \alpha \,\Delta T \tag{1}$$

Where  $\Delta \alpha$  is difference in thermal expansion coefficient in K<sup>-1</sup> between substrate and film ( $\Delta \alpha = \alpha_s - \alpha_f$ ),  $\Delta T$  is change in temperature, *E* is Youngs Modulus. For Silicon thermal stress is 431 MPa and 814.3 MPa for GaAs. Since the two materials are considered isotropic ( $\epsilon = \epsilon_x = \epsilon_y$ ,  $\sigma = \sigma_x = \sigma_y$ ), the misfit stress in the upper layer is

$$\sigma^{T} = \frac{-E_{i}(\alpha_{i} - \alpha_{s})}{(1 - \nu_{i})} * \left(T - T_{0}^{i}\right) + \sigma_{i}^{I}$$

$$\tag{2}$$

Where i denotes layer number, normally this is the stress present in upper layer when the substrate is ultimately thick compared to film thickness,  $h_s/h_f <<<1$ . The equations for top film stress  $\sigma$  and average film stress  $\overline{\sigma}$  are related to film/substrate thickness ratio ( $\xi=h_f/h_s$ ) and Biaxial Young's Modulus ratio  $\Sigma = \frac{E_2/(1-\nu_2)}{E_1/(1-\nu_1)}$  as seen in (Hutchinson [1996]). Equations for top film stress  $\sigma$  and average film stress $\overline{\sigma}$  are given by the following relations [6]

$$\frac{\overline{\sigma}}{\sigma^T} = \frac{1 + \Sigma \xi^3}{(\Sigma \xi^2 - 1)^2 + 4\Sigma \xi (\xi + 1)^2} \tag{3}$$

$$\frac{\sigma}{\sigma^{T}} = \frac{1 - 3\Sigma\xi^{2} - 2\Sigma\xi^{3}}{(\Sigma\xi^{2} - 1)^{2} + 4\Sigma\xi(\xi + 1)^{2}}$$

(4)

The curvature of the bilayer could be concluded as

$$\kappa = \frac{1+\xi}{1+\Sigma\xi^3} * \frac{6(1-\nu_1)h_2\overline{\sigma}}{E_1h_1^2}$$

(5)

The curvature of the bilayer could also be calculated. Radius of curvature  $\rho=1/\kappa$ , where  $\kappa$  is in mm. Mismatch stress in GaAs layer is 653.9 MPa with a negative sign indicating compression, while stress at film top is 226 MPa, higher by 50 MPa than that obtained from simulation, and average film stress is 286.6 MPa. Curvature Value is 232 corresponding to a curvature radius of 4.32 mm. Applying basic Pythagoras Theorem on nodal displacement on model without voids, curvature of radius was found to be 5.24 mm. While a radius of 7.03 mm was obtained for voided model. Curvature radius indicates the variation of the unit tangent direction, the higher the curvature radius, the less the deflection.

Figure2Von Mises Stress Average 75% without voids

Figure5Spatial Displacement with Voids

# IV. CONCLUSION

In conclusion, thermal stresses and therefore dislocations have shown reduction when voids where introduced near the interface of GaAs/Si cell. The paper discussed two elastic models illustrating void effect on dislocation density. A reduction in stress at Si layer of 14% while GaAs stresses rose to 18%, reduction in maximum displacement is 11%. The approach may address a solution for the 1.0 eV sub cell problem; permitting an efficiency raise to 45%. Void density and positioning should be controlled for stress reduction.

| Appendix         |                      |                     |                     |

|------------------|----------------------|---------------------|---------------------|

| Table I          |                      |                     |                     |

| Parameter        | Si                   | GaAs                | Unit                |

| Young's Modulus  | 168.9                | 144                 | GPa                 |

| Poisson's Ratio  | 0.262                | 0.31                |                     |

| Density          | 2.33e <sup>-9</sup>  | 5.32e <sup>-9</sup> | ton/mm <sup>3</sup> |

| CTE (a)          | $2.616 e^{-6}$       | $5.8 e^{-6}$        | $K^{-1}$            |

| Slip System      | {111}                | {111}               |                     |

|                  | $< \overline{1}10 >$ | <110>               |                     |

| Lattice Constant | 0.543106             | 0.56533             | nm                  |

#### ACKNOWLEDGMENT

The support from North Carolina State University Laboratory is greatly appreciated.

#### Refrences

- M. Wanlas *et al.*"Monolithic, ultra-thin GaInP/GaAs/GaInAs tandem solar cells", Photovoltaic Energy Conversion-IEEE 4th World Conference. 1, 2006,729.

- [2] N. Ekins-Daukes*et al.* "Strain balanced GaAsP/InGaAs quantum well solar cells", Appl. Phys. Lett. 75 (26), 1999, 4195.

- [3] T.Katsuyama, S. M.Bedair, N. C.Giles, R. P.Burns, and J. F.Schetzina "Growth and characterization of InGaAs/GaAsP strained layer superlattices", J. Appl. Phys. 62 (2), 1987, 498.

- [4] P.Frajtag *et al.* "Improved light-emitting diode performance by conformal overgrowth of multiple quantum wells and fully coalesced p-type GaN on GaN nanowires", Appl. Phys. Lett. 98, 2011, 143014.

- [5] P.Frajtag,N.A.El-Masry, N.Nepal, S.M.Bedair, Applied Physics Letters 98, 2011, 023115.

- [6] J. W. Hutchinson "Stresses and Failure Modes in Thin Films and Multilayers", Stresses in films and multilayers, 1996.