## **RECENT ADVANCES in CIRCUITS**

Proceedings of the 19th International Conference on Circuits (part of CSCC '15)

> Zakynthos Island, Greece July 16-20, 2015

# **RECENT ADVANCES in CIRCUITS**

Proceedings of the 19th International Conference on Circuits (part of CSCC '15)

Zakynthos Island, Greece July 16-20, 2015

#### Copyright © 2015, by the editors

All the copyright of the present book belongs to the editors. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the editors.

All papers of the present volume were peer reviewed by no less than two independent reviewers. Acceptance was granted when both reviewers' recommendations were positive.

Series: Recent Advances in Electrical Engineering Series | 51

ISSN: 1790-5117 ISBN: 978-1-61804-319-1

# **RECENT ADVANCES in CIRCUITS**

Proceedings of the 19th International Conference on Circuits (part of CSCC '15)

> Zakynthos Island, Greece July 16-20, 2015

## **Organizing Committee**

#### Editor:

Prof. Valeri Mladenov, Technical University of Sofia, Bulgaria

#### Associate Editors:

Prof. Dora Foti Prof. Dorota Jelonek

#### **Organizing Committee:**

Prof. Kleanthis Psarris, The City University of New York, USA (General Chair)

Prof. Pierre Borne, IEEE France Section Chair, IEEE Fellow, Ec Centr de Lille, France (General Chair)

Prof. Panos M. Pardalos, University of Florida, USA (Co-Chair)

Prof. George Vachtsevanos, Georgia Institute of Technology, Atlanta, Georgia, USA (Co-Chair)

Prof. Tadeusz Kaczorek, IEEE Fellow, Warsaw University of Technology, Poland (Co-Chair)

Prof. Nikos Mastorakis, Technical University of Sofia, Bulgaria (Program Chair)

Prof. Branimir Reljin, University of Belgrade, Belgrade, Serbia (International Liaisons)

Prof. Valeri Mladenov, Technical University of Sofia, Bulgaria (Publicity Chair)

Prof. Imre Rudas, Obuda University, Budapest, Hungary (Tutorials Chair)

Prof. Vladimir Vasek, Tomas Bata University, Zlin, Czech Republic (Special Sessions Chair)

Prof. Anca Croitoru, Al.I. Cuza University, Iasi, Romania (Workshops Chair)

#### **Steering Committee:**

Prof. Yuriy S. Shmaliy, IEEE Fellow, Universidad de Guanajuato, Mexico

Prof. Alaa Khamis, IEEE Robotics and Automation Egypt-Chapter Chair, Egypt

Prof. Ioannis Stathopulos, Technical University of Athens, Greece

Prof. Charalambos Arapatsakos, University of Thrace, Greece

Prof. Fragkiskos Topalis, Technical University of Athens, Greece

Prof. Klimis Ntalianis, Technological Educational Institute of Athens, Greece

Prof. Eduardo Mario Dias, University of Sao Paulo, Brazil

Prof. Miroslav Voznak, VSB-Technical University of Ostrava, Czech Republic

Prof. Abdel-Badeeh M. Salem, Ain Shams University, Cairo, Egypt

Prof. Nikolaos Bardis, M.Inst. of Univ. Educ. (ASEI), Hellenic Army Academy, Athens, Greece

Prof. Antoanela Naaji, Vasile Goldis Western University Arad, Romania

Prof. Elena Zamiatina, Perm State University, Perm Krai, Russia

Prof. Pan Agathoklis, University of Victoria, Canada

Prof. George Tsekouras, M.Inst. of Univ. Educ. (ASEI), Hellenic Naval Academy, Athens, Greece

Prof. Claudio Talarico, Gonzaga University, Spokane, USA

## International Scientific Committee:

Prof. Lotfi Zadeh (IEEE Fellow, University of Berkeley, USA)

Prof. Leon Chua (IEEE Fellow, University of Berkeley, USA)

Prof. Michio Sugeno (RIKEN Brain Science Institute (RIKEN BSI), Japan)

Prof. Dimitri Bertsekas (IEEE Fellow, MIT, USA)

Prof. Demetri Terzopoulos (IEEE Fellow, ACM Fellow, UCLA, USA)

Prof. Georgios B. Giannakis (IEEE Fellow, University of Minnesota, USA)

Prof. Abraham Bers (IEEE Fellow, MIT, USA)

Prof. Brian Barsky (IEEE Fellow, University of Berkeley, USA)

Prof. Aggelos Katsaggelos (IEEE Fellow, Northwestern University, USA)

Prof. Josef Sifakis (Turing Award 2007, CNRS/Verimag, France)

Prof. Kinshuk (Fellow IEEE, Massey Univ. New Zeland),

Prof. Leonid Kazovsky (Stanford University, USA)

Prof. Narsingh Deo (IEEE Fellow, ACM Fellow, University of Central Florida, USA) Prof. Kamisetty Rao (Fellow IEEE, Univ. of Texas at Arlington, USA) Prof. Anastassios Venetsanopoulos (Fellow IEEE, University of Toronto, Canada) Prof. Steven Collicott (Purdue University, West Lafayette, IN, USA) Prof. Nikolaos Paragios (Ecole Centrale Paris, France) Prof. Nikolaos G. Bourbakis (IEEE Fellow, Wright State University, USA) Prof. Stamatios Kartalopoulos (IEEE Fellow, University of Oklahoma, USA) Prof. Irwin Sandberg (IEEE Fellow, University of Texas at Austin, USA), Prof. Michael Sebek (IEEE Fellow, Czech Technical University in Prague, Czech Republic) Prof. Hashem Akbari (University of California, Berkeley, USA) Prof. Lei Xu (IEEE Fellow, Chinese University of Hong Kong, Hong Kong) Prof. Paul E. Dimotakis (California Institute of Technology Pasadena, USA) Prof. Martin Pelikan (UMSL, USA) Prof. Patrick Wang (MIT, USA) Prof. Wasfy B Mikhael (IEEE Fellow, University of Central Florida Orlando, USA) Prof. Sunil Das (IEEE Fellow, University of Ottawa, Canada) Prof. Nikolaos D. Katopodes (University of Michigan, USA) Prof. Bimal K. Bose (Life Fellow of IEEE, University of Tennessee, Knoxville, USA) Prof. Janusz Kacprzyk (IEEE Fellow, Polish Academy of Sciences, Poland) Prof. Sidney Burrus (IEEE Fellow, Rice University, USA) Prof. Biswa N. Datta (IEEE Fellow, Northern Illinois University, USA) Prof. Mihai Putinar (University of California at Santa Barbara, USA) Prof. Wlodzislaw Duch (Nicolaus Copernicus University, Poland) Prof. Michael N. Katehakis (Rutgers, The State University of New Jersey, USA) Prof. Pan Agathoklis (Univ. of Victoria, Canada) Dr. Subhas C. Misra (Harvard University, USA) Prof. Martin van den Toorn (Delft University of Technology, The Netherlands) Prof. Malcolm J. Crocker (Distinguished University Prof., Auburn University, USA) Prof. Urszula Ledzewicz, Southern Illinois University, USA. Prof. Dimitri Kazakos, Dean, (Texas Southern University, USA) Prof. Ronald Yager (Iona College, USA) Prof. Athanassios Manikas (Imperial College, London, UK) Prof. Keith L. Clark (Imperial College, London, UK) Prof. Argyris Varonides (Univ. of Scranton, USA) Dr. Michelle Luke (Univ. Berkeley, USA) Prof. Patrice Brault (Univ. Paris-sud, France) Prof. Jim Cunningham (Imperial College London, UK) Prof. Philippe Ben-Abdallah (Ecole Polytechnique de l'Universite de Nantes, France) Prof. Ichiro Hagiwara, (Tokyo Institute of Technology, Japan) Prof. Akshai Aggarwal (University of Windsor, Canada) Prof. Ulrich Albrecht (Auburn University, USA) Prof. Alexey L Sadovski (IEEE Fellow, Texas A&M University, USA) Prof. Amedeo Andreotti (University of Naples, Italy) Prof. Ryszard S. Choras (University of Technology and Life Sciences Bydgoszcz, Poland) Prof. Remi Leandre (Universite de Bourgogne, Dijon, France) Prof. Moustapha Diaby (University of Connecticut, USA) Prof. Brian McCartin (New York University, USA) Prof. Anastasios Lyrintzis (Purdue University, USA) Prof. Charles Long (Prof. Emeritus University of Wisconsin, USA) Prof. Marvin Goldstein (NASA Glenn Research Center, USA) Prof. Ron Goldman (Rice University, USA) Prof. Ioannis A. Kakadiaris (University of Houston, USA) Prof. Richard Tapia (Rice University, USA) Prof. Milivoje M. Kostic (Northern Illinois University, USA)

Prof. Helmut Jaberg (University of Technology Graz, Austria) Prof. Ardeshir Anjomani (The University of Texas at Arlington, USA) Prof. Heinz Ulbrich (Technical University Munich, Germany) Prof. Reinhard Leithner (Technical University Braunschweig, Germany) Prof. M. Ehsani (Texas A&M University, USA) Prof. Sesh Commuri (University of Oklahoma, USA) Prof. Nicolas Galanis (Universite de Sherbrooke, Canada) Prof. Rui J. P. de Figueiredo (University of California, USA) Prof. Hiroshi Sakaki (Meisei University, Tokyo, Japan) Prof. K. D. Klaes, (Head of the EPS Support Science Team in the MET Division at EUMETSAT, France) Prof. Emira Maljevic (Technical University of Belgrade, Serbia) Prof. Kazuhiko Tsuda (University of Tsukuba, Tokyo, Japan) Prof. Nobuoki Mano (Meisei University, Tokyo, Japan) Prof. Nobuo Nakajima (The University of Electro-Communications, Tokyo, Japan) Prof. P. Vanderstraeten (Brussels Institute for Environmental Management, Belgium) Prof. Annaliese Bischoff (University of Massachusetts, Amherst, USA) Prof. Fumiaki Imado (Shinshu University, Japan) Prof. Sotirios G. Ziavras (New Jersey Institute of Technology, USA) Prof. Marc A. Rosen (University of Ontario Institute of Technology, Canada) Prof. Thomas M. Gatton (National University, San Diego, USA) Prof. Leonardo Pagnotta (University of Calabria, Italy) Prof. Yan Wu (Georgia Southern University, USA) Prof. Daniel N. Riahi (University of Texas-Pan American, USA) Prof. Alexander Grebennikov (Autonomous University of Puebla, Mexico) Prof. Bennie F. L. Ward (Baylor University, TX, USA) Prof. Guennadi A. Kouzaev (Norwegian University of Science and Technology, Norway) Prof. Geoff Skinner (The University of Newcastle, Australia) Prof. Hamido Fujita (Iwate Prefectural University(IPU), Japan) Prof. Francesco Muzi (University of L'Aquila, Italy) Prof. Claudio Rossi (University of Siena, Italy) Prof. Sergey B. Leonov (Joint Institute for High Temperature Russian Academy of Science, Russia) Prof. Lili He (San Jose State University, USA) Prof. M. Nasseh Tabrizi (East Carolina University, USA) Prof. Alaa Eldin Fahmy (University Of Calgary, Canada) Prof. Gh. Pascovici (University of Koeln, Germany) Prof. Pier Paolo Delsanto (Politecnico of Torino, Italy) Prof. Radu Munteanu (Rector of the Technical University of Cluj-Napoca, Romania) Prof. Ioan Dumitrache (Politehnica University of Bucharest, Romania) Prof. Miquel Salgot (University of Barcelona, Spain) Prof. Amaury A. Caballero (Florida International University, USA) Prof. Maria I. Garcia-Planas (Universitat Politecnica de Catalunya, Spain) Prof. Petar Popivanov (Bulgarian Academy of Sciences, Bulgaria) Prof. Alexander Gegov (University of Portsmouth, UK) Prof. Lin Feng (Nanyang Technological University, Singapore) Prof. Colin Fyfe (University of the West of Scotland, UK) Prof. Zhaohui Luo (Univ of London, UK) Prof. Wolfgang Wenzel (Institute for Nanotechnology, Germany) Prof. Weilian Su (Naval Postgraduate School, USA) Prof. Phillip G. Bradford (The University of Alabama, USA) Prof. Hamid Abachi (Monash University, Australia) Prof. Josef Boercsoek (Universitat Kassel, Germany) Prof. Eyad H. Abed (University of Maryland, Maryland, USA) Prof. Andrzej Ordys (Kingston University, UK) Prof. T Bott (The University of Birmingham, UK)

Prof. T.-W. Lee (Arizona State University, AZ, USA) Prof. Le Yi Wang (Wayne State University, Detroit, USA) Prof. Oleksander Markovskyy (National Technical University of Ukraine, Ukraine) Prof. Suresh P. Sethi (University of Texas at Dallas, USA) Prof. Hartmut Hillmer(University of Kassel, Germany) Prof. Bram Van Putten (Wageningen University, The Netherlands) Prof. Alexander Iomin (Technion - Israel Institute of Technology, Israel) Prof. Roberto San Jose (Technical University of Madrid, Spain) Prof. Minvydas Ragulskis (Kaunas University of Technology, Lithuania) Prof. Arun Kulkarni (The University of Texas at Tyler, USA) Prof. Joydeep Mitra (New Mexico State University, USA) Prof. Vincenzo Niola (University of Naples Federico II, Italy) Prof. S. Y. Chen, (Zhejiang University of Technology, China and University of Hamburg, Germany) Prof. Duc Nguyen (Old Dominion University, Norfolk, USA) Prof. Tuan Pham (James Cook University, Townsville, Australia) Prof. Jiri Klima (Technical Faculty of CZU in Prague, Czech Republic) Prof. Rossella Cancelliere (University of Torino, Italy) Prof. Wladyslaw Mielczarski (Technical University of Lodz, Poland) Prof. Ibrahim Hassan (Concordia University, Montreal, Quebec, Canada) Prof. Erich Schmidt (Vienna University of Technology, Austria) Prof. James F. Frenzel (University of Idaho, USA) Prof. Vilem Srovnal, (Technical University of Ostrava, Czech Republic) Prof. J. M. Giron-Sierra (Universidad Complutense de Madrid, Spain) Prof. Rudolf Freund (Vienna University of Technology, Austria) Prof. Alessandro Genco (University of Palermo, Italy) Prof. Martin Lopez Morales (Technical University of Monterey, Mexico) Prof. Ralph W. Oberste-Vorth (Marshall University, USA)

Prof. Photios Anninos, Democritus University of Thrace, Greece

## **Additional Reviewers**

**Bazil Taha Ahmed** James Vance Sorinel Oprisan M. Javed Khan Jon Burley Xiang Bai Hessam Ghasemnejad Angel F. Tenorio Yamagishi Hiromitsu Imre Rudas Takuya Yamano Abelha Antonio Andrey Dmitriev Valeri Mladenov Francesco Zirilli **Ole Christian Boe** Masaji Tanaka Jose Flores Kazuhiko Natori Matthias Buyle Frederic Kuznik Minhui Yan Eleazar Jimenez Serrano Konstantin Volkov **Miguel Carriegos** Zhong-Jie Han Francesco Rotondo George Barreto Moran Wang Alejandro Fuentes-Penna Shinji Osada Kei Eguchi **Philippe Dondon** Dmitrijs Serdjuks Deolinda Rasteiro **Stavros Ponis** Tetsuya Shimamura João Bastos Gengi Xu Santoso Wibowo Tetsuya Yoshida José Carlos Metrôlho

Universidad Autonoma de Madrid, Spain The University of Virginia's College at Wise, VA, USA College of Charleston, CA, USA Tuskegee University, AL, USA Michigan State University, MI, USA Huazhong University of Science and Technology, China Kingston University London, UK Universidad Pablo de Olavide, Spain Ehime University, Japan Obuda University, Budapest, Hungary Kanagawa University, Japan Universidade do Minho, Portugal Russian Academy of Sciences, Russia Technical University of Sofia, Bulgaria Sapienza Universita di Roma, Italy Norwegian Military Academy, Norway Okayama University of Science, Japan The University of South Dakota, SD, USA Toho University, Japan Artesis Hogeschool Antwerpen, Belgium National Institute of Applied Sciences, Lyon, France Shanghai Maritime University, China Kyushu University, Japan Kingston University London, UK Universidad de Leon, Spain Tianjin University, China Polytechnic of Bari University, Italy Pontificia Universidad Javeriana, Colombia Tsinghua University, China Universidad Autónoma del Estado de Hidalgo, Mexico Gifu University School of Medicine, Japan Fukuoka Institute of Technology, Japan Institut polytechnique de Bordeaux, France Riga Technical University, Latvia Coimbra Institute of Engineering, Portugal National Technical University of Athens, Greece Saitama University, Japan Instituto Superior de Engenharia do Porto, Portugal Tianjin University, China CQ University, Australia Hokkaido University, Japan Instituto Politecnico de Castelo Branco, Portugal

## **Table of Contents**

| Plenary Lecture 1: Error Estimation in the Decoupling of III-Defined and/or Perturbed<br>Nonlinear Processes                                                                         | 14 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Pierre Borne                                                                                                                                                                         |    |

| Plenary Lecture 2: Applications of Linear Algebra in Signal Processing, Wireless<br>Communications and Bioinformatics<br>Erchin Serpedin                                             | 16 |

| Plenary Lecture 3: Reliability Life Cycle Management for Engineered Systems<br>George Vachtsevanos                                                                                   | 17 |

| Plenary Lecture 4: Augmented Reality: The Emerging Trend in Education<br>Minjuan Wang                                                                                                | 19 |

| Plenary Lecture 5: Application of Multivariate Empirical Mode Decomposition in EEG<br>Signals for Subject Independent Affective States Classification<br>Konstantinos N. Plataniotis | 21 |

| Plenary Lecture 6: State of the Art and Recent Progress in Uncertainty Quantification for Electronic Systems (i.e. Variation-Aware or Stochastic Simulation)<br>Luca Daniel          | 23 |

| Distributed Power Generation Using Small Wind Turbine Systems: New Chaotic Attractor<br>in Back-to-Back Converter Dynamics<br>Donato Cafagna, Giuseppe Grassi                        | 25 |

| High-Impedance Electrode Contact Monitoring<br>M. J. Burke, C. Molloy, H. Fossan                                                                                                     | 31 |

| Adaptive Control of Temperature Inside Plugflow Chemical Reactor with Pole-Placement<br>Method and LQ Approach<br>Jiri Vojtesek, Petr Dostal                                         | 37 |

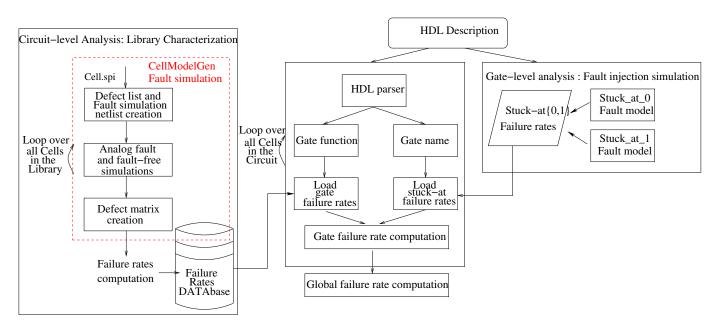

| A Methodology for Accurate Defect Tolerance Analysis<br>Mariem Slimani, Arwa Ben Dhia, Lirida Naviner                                                                                | 43 |

| Magnus Effect in the Fluid-Film Bearings<br>L. Savin, A. Kornaev, E. Kornaeva, O. Savina                                                                                             | 50 |

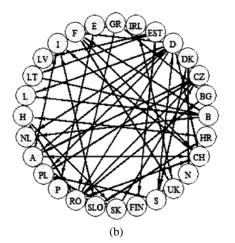

| On Modeling European Energy Exchanges as Small-World Phenomena<br>Leonarda Carnimeo, Michele Dassisti                                                                                | 55 |

| Recent Advances in Circuits |

|-----------------------------|

|-----------------------------|

| Electric Vehicle Speed Control Using Three Phase Inverter Operated by DSP-Based Vector<br>Pulse Width Modulation Technique                                             | 59  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Saidi Hemza, Noureddine Mansour, Midoun Abdelhamid                                                                                                                     |     |

| VLSI Implementation of an Improved Multiplier for FFT Computation in Biomedical<br>Applications                                                                        | 66  |

| Arathi Ajay, R. Mary Lourde                                                                                                                                            |     |

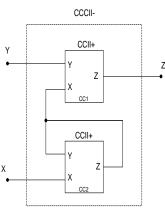

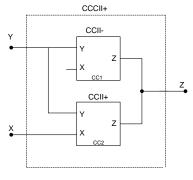

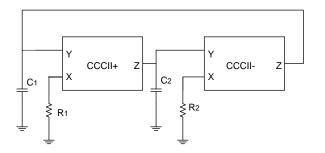

| Realization of Tuneable MOS-C Quadrature Sinusoidal Oscillator Using Composite Current Conveyor                                                                        | 73  |

| Hasan Çiçekli, Ahmet Gökçen                                                                                                                                            |     |

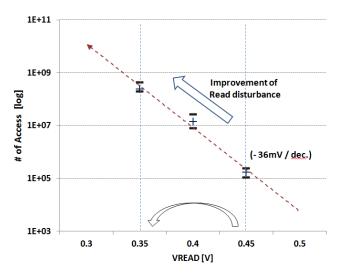

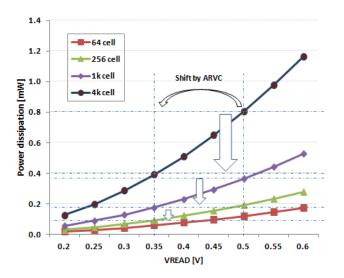

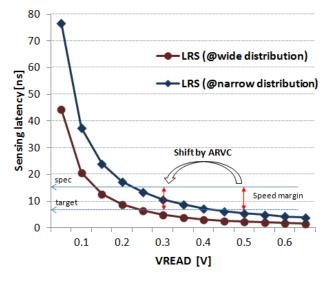

| Adaptive Read Voltage Control for Improvement of Read Disturbance and Power<br>Consumption in Cross-Point ReRAM                                                        | 77  |

| Jong-Min Bang, Wen-Liang Ma, Sang-Yun Kim, Jong-Min Baek, Kee-Won Kwon                                                                                                 |     |

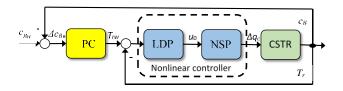

| Cascade Nonlinear Control of a Continuous Stirred Tank Reactor<br>Petr Dostál, Vladimír Bobál, Jiří Vojtěšek                                                           | 81  |

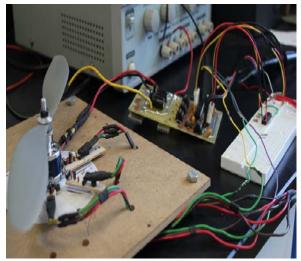

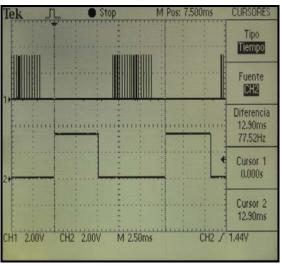

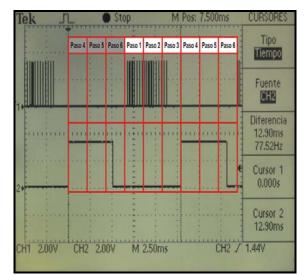

| Circuitry Design for Small Energy Harvest System                                                                                                                       | 87  |

| Yung Ting, Chih Hsuan Yu, Louel Lacasandile, Jia Ci Chen                                                                                                               | 07  |

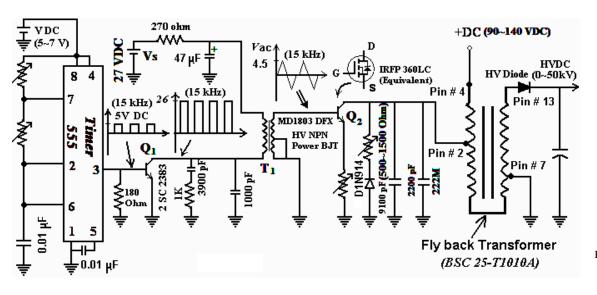

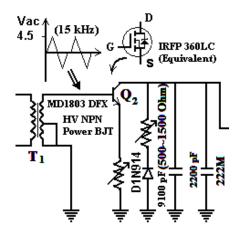

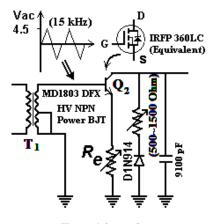

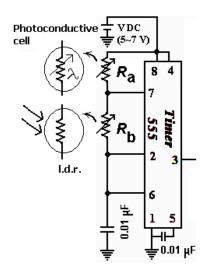

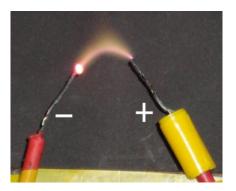

| An Adjustable HVDC Power Supply Using Integrated High Voltage Transformer with Some<br>Protective & Controlling Features<br>Nader N. Barsoum, Muhammad Muktadir Rahman | 91  |

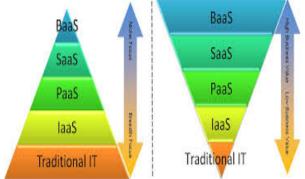

| Internet Traffic Trends and Major Security Challenges in Local & Internet Cloud<br>Gasim Alandjani, Shahbaz Pervez, Qurrat Ulain                                       | 96  |

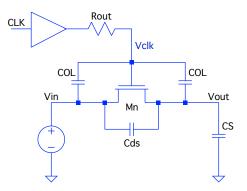

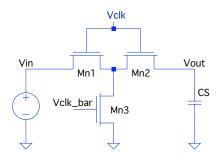

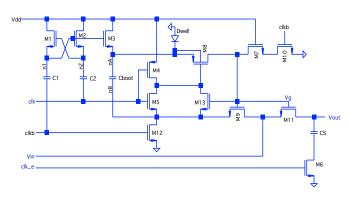

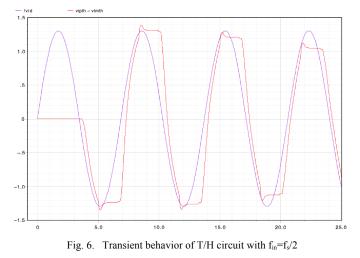

| Design and Optimization of a 300 MSamples/s Track and Hold Architecture for a 5-Bit<br>Flash ADC in 180nm CMOS Technology<br>C. Talarico, D. Villamizar                | 101 |

| Electronic Speed Variator for a Brushless DC Motor                                                                                                                     | 106 |

| Jorge M. Jaimes Ponce, Jesús U. Liceaga C., Irma I. Siller A., Enrique Arévalo Zamudio                                                                                 | 100 |

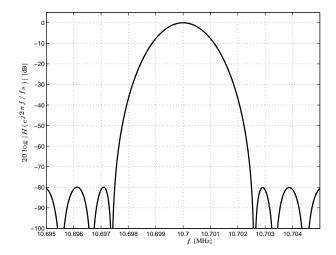

| Improved Design of Optimal Narrow Band-Pass FIR Filters<br>Pavel Zahradnik, Michal Šusta, Boris Šimak, Miroslav Vlček                                                  | 111 |

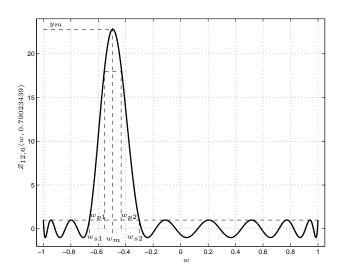

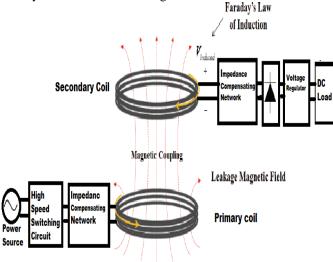

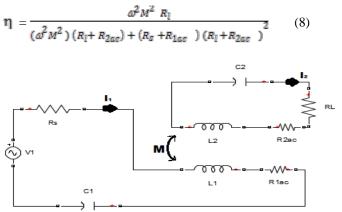

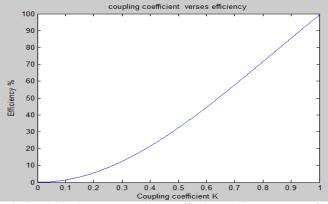

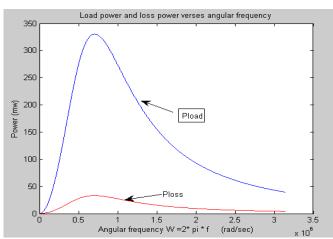

| Wireless Power Transfer through Inductive Coupling<br>Mohamed A. Hassan, A. Elzawawi                                                                                   | 115 |

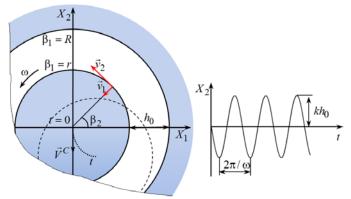

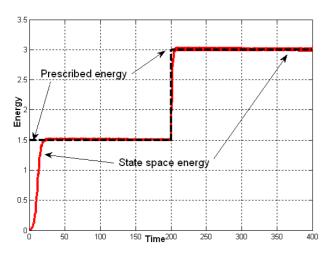

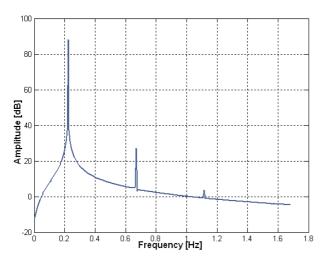

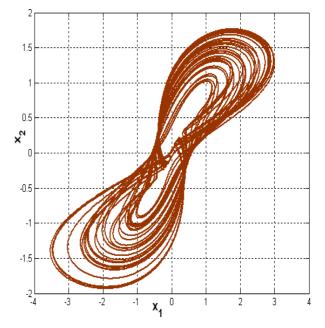

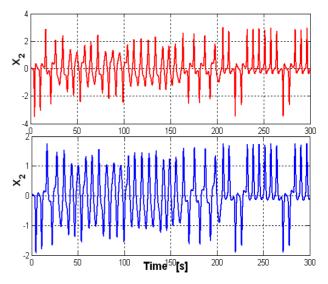

| Oscillator and Chaotic System Based on State Space Energy Feedback<br>M. Stork                                                                                         | 119 |

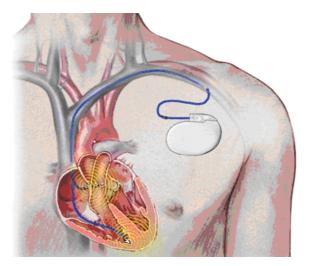

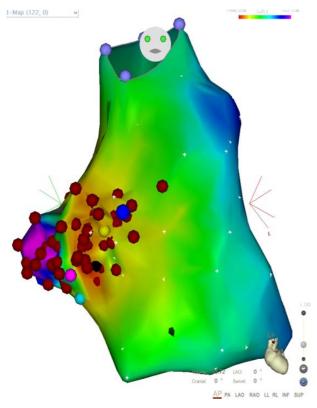

| Optimization of Pacemaker Leads Place Based on Vectorcardiography Signal Processing                                                                                    | 125 |

M. Stork, V. Vancura

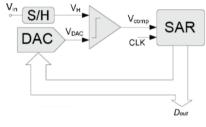

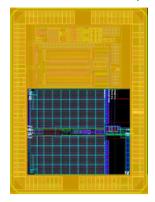

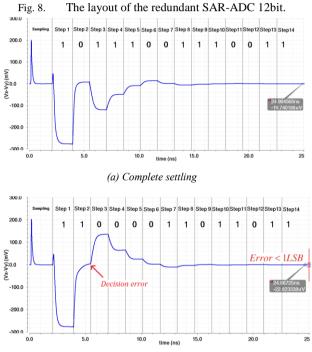

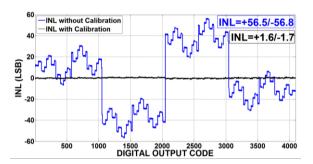

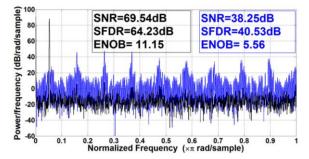

| A 12bits 40MSPS SAR ADC with a Redundancy Algorithm and Digital Calibration for the ATLAS- LArg Calorimeter Readout                                                   | 129 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Mohamed Zeloufi, Daniel Dzahini, Fatah Ellah Rarbi                                                                                                                    |     |

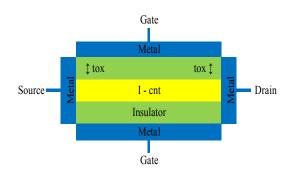

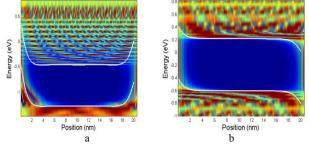

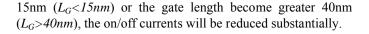

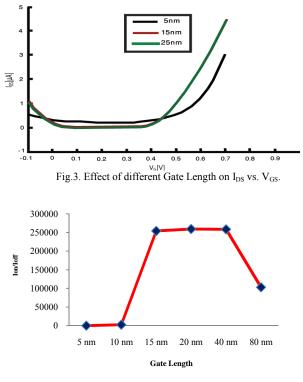

| On/Off Ratio Tuning of Schottky Barrier CNTFETs Based on Quantum Simulation<br>Approach                                                                               | 133 |

| Amin Ghasemi Nejad Raeini, Hosein Eslami, Mostafa Alibeygi, Hamdollah Dehghani                                                                                        |     |

| Quantum Simulation of Double Halo Schottky Barrier CNTFET (DH_SB_CNTFET)<br>Amin Ghasemi Nejad Raeini, Zoheir Kordrostami, Ahmad Rafizadeh, Morteza Faghei            | 136 |

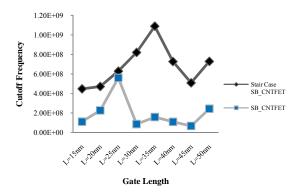

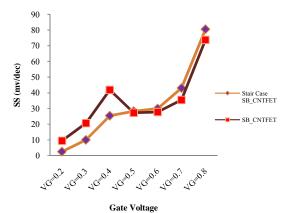

| Performance Optimization of Conventional Schottky Barrier CNTFETs Based on Stair-Case<br>Halo Doping Strategy                                                         | 140 |

| Amin Ghasemi Nejad Raeini, Zoheir Kordrostami, M. H. Shekari, H. Sadeghi                                                                                              |     |

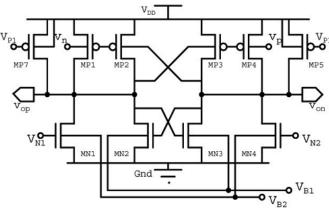

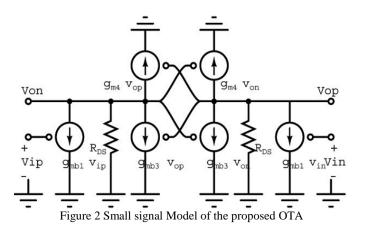

| <b>A Novel 0.5V Bulk Driven Pseudo-Differential OTA</b><br>Antaryami Panigrahi, Abhipsa Parhi                                                                         | 144 |

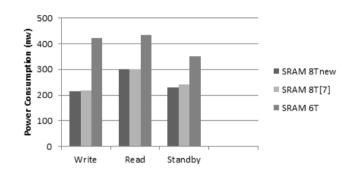

| A Novel Design of Low-Power SRAM Cell<br>Setareh Ghorbanian, Seyyed Reza Talebiyan                                                                                    | 148 |

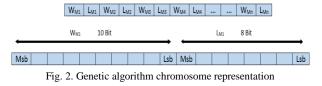

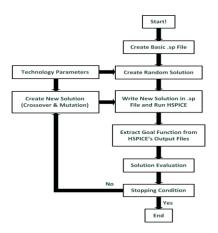

| A Novel Method for Transistor Sizing in Digital Circuits by Artificial Intelligence<br>Eghbal Rahimi, Seyyed Reza Talebiyan                                           | 152 |

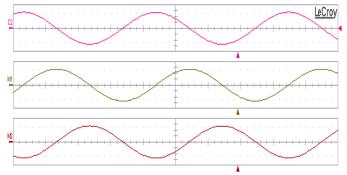

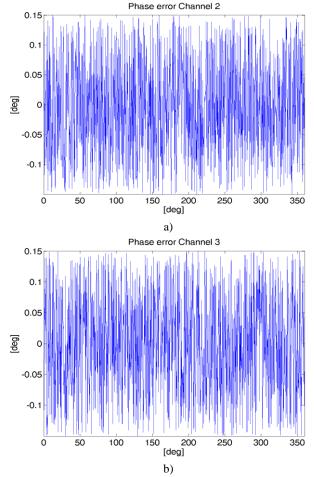

| A 10-Bits Three Channels Phase Shifter Integrated Circuit for Active Electronic Scanned<br>Array Applications<br>G. Coviello, G. Piccinni, G. Avitabile, N. Margiotta | 156 |

|                                                                                                                                                                       |     |

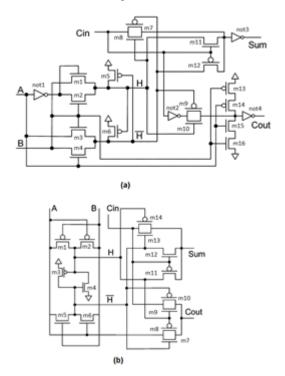

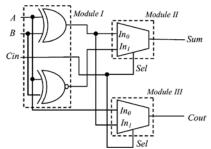

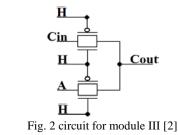

| Design of High Performance and Low Power 16T Full Adder Cells for Subthreshold Voltage Technology                                                                     | 161 |

| Ebrahim Pakniyat, Seyyed Reza Talebiyan                                                                                                                               |     |

| Design of New Low-Power High-Performance Full Adder Cell Using Hybrid-CMOS Logic<br>Style                                                                             | 166 |

| Milad Jalalian, Seyed Reza Talebiyan, Ebrahim Pakniyat                                                                                                                |     |

| Influence of Parametric Uncertainties on Control Quality of Time-Delay Processes<br>V. Bobál, P. Dostál, M. Kubalčík                                                  | 170 |

| Authors Index                                                                                                                                                         | 176 |

## **Plenary Lecture 1**

## Error Estimation in the Decoupling of Ill-Defined and/or Perturbed Nonlinear Processes

## Professor Pierre Borne (IEEE Fellow) Co-authors Amira Gharbi, Mohamed Benrejeb Centre de Recherche en Informatique Signal et Automatique de Lille, CRIStAL Ecole Centrale de Lille France E-mail: pierre.borne@ec-lille.fr

**Abstract:** This lecture deals with the definition of the attractors characterizing the precision of decoupling control laws for a nonlinear process in presence of uncertainties and/or bounded perturbations. This approach is based on the use of aggregation techniques and the definition of a comparison system of the controlled process.

Brief Biography of the Speaker: Pierre BORNE received the Master degree of Physics in 1967 and the Master of Electrical Engineering, the Master of Mechanics and the Master of Applied Mathematics in 1968. The same year he obtained the Diploma of "Ingenieur IDN" (French "Grande Ecole"). He obtained the PhD in Automatic Control of the University of Lille in 1970 and the DSc in physics of the same University in 1976. Dr BORNE is author or co-author of about 200 Publications and book chapters and of about 300 communications in international conferences. He is author of 18 books in Automatic Control, co-author of an english-french, french-english « Systems and Control » dictionary and co-editor of the "Concise Encyclopedia of Modelling and Simulation" published with Pergamon Press. He is Editor of two book series in French and coeditor of a book series in English. He has been invited speaker for 40 plenary lectures or tutorials in International Conferences. He has been supervisor of 76 PhD Thesis and member of the committee for about 300 doctoral thesis . He has participated to the editorial board of 20 International Journals including the IEEE, SMC Transactions, and of the Concise Subject Encyclopedia . Dr BORNE has organized 15 international conferences and symposia, among them the 12th and the 17 th IMACS World Congresses in 1988 and 2005, the IEEE/SMC Conferences of 1993 (Le Touquet – France) and of 2002 (Hammamet - Tunisia), the CESA IMACS/IEEE-SMC multiconferences of 1996 (Lille – France), of 1998 (Hammamet – Tunisia), of 2003 (Lille-France ) and of 2006 (Beijing, China) and the 12th IFAC LSS symposium (Lille France, 2010) He was chairman or co-chairman of the IPCs of 34 international conferences (IEEE, IMACS, IFAC) and member of the IPCs of more than 200 international conferences. He was the editor of many volumes and CDROMs of proceedings of conferences. Dr BORNE has participated to the creation and development of two groups of research and two doctoral formations (in Casablanca, Morocco and in Tunis, Tunisia). twenty of his previous PhD students are now full Professors (in France, Morocco, Tunisia, and Poland). In the IEEE/SMC Society Dr BORNE has been AdCom member (1991-1993 ; 1996-1998), Vice President for membership

#### Recent Advances in Circuits

(1992-1993) and Vice President for conferences and meetings (1994-1995, 1998-1999). He has been associate editor of the IEEE Transactions on Systems Man and Cybernetics (1992-2001). Founder of the SMC Technical committee « Mathematical Modelling » he has been president of this committee from 1993 to 1997 and has been president of the « System area » SMC committee from 1997 to 2000. He has been President of the SMC Society in 2000 and 2001, President of the SMC-nomination committee in 2002 and 2003 and President of the SMC-Awards and Fellows committee in 2004 and 2005. He is member of the Advisory Board of the "IEEE Systems Journal". Dr. Borne received in 1994, 1998 and 2002 Outstanding Awards from the IEEE/SMC Society and has been nominated IEEE Fellow the first of January 1996. He received the Norbert Wiener Award from IEEE/SMC in 1998, the Third Millennium Medal of IEEE in 2000 and the IEEE/SMC Joseph G. Wohl Outstanding Career Award in 2003. He has been vice president of the "IEEE France Section" (2002-2010) and is president of this section since 2011. He has been appointed in 2007 representative of the Division 10 of IEEE for the Region 8 Chapter Coordination sub-committee (2007-2008) He has been member of the IEEE Fellows Committee (2008- 2010) Dr BORNE has been IMACS Vice President (1988-1994). He has been co-chairman of the IMACS Technical Committee on "Robotics and Control Systems" from 1988 to 2005 and in August 1997 he has been nominated Honorary Member of the IMACS Board of Directors. He is since 2008 vice-president of the IFAC technical committee on Large Scale Systems. Dr BORNE is Professor "de Classe Exceptionnelle" at the "Ecole Centrale de Lille" where he has been Head of Research from 1982 to 2005 and Head of the Automatic Control Department from 1982 to 2009. His activities concern automatic control and robust control including implementation of soft computing techniques and applications to large scale and manufacturing systems. He was the principal investigator of many contracts of research with industry and army (for more than three millions €) Dr BORNE is "Commandeur dans l'Ordre des Palmes Acad?miques" since 2007. He obtained in 1994 the french "Kulman Prize". Since 1996, he is Fellow of the Russian Academy of Non-Linear Sciences and Permanent Guest Professor of the Tianjin University (China). In July 1997, he has been nominated at the "Tunisian National Order of Merit in Education" by the Republic of Tunisia. In June 1999 he has been nominated « Professor Honoris Causa » of the National Institute of Electronics and Mathematics of Moscow (Russia) and Doctor Honoris Causa of the same Institute in October 1999. In 2006 he has been nominated Doctor Honoris Causa of the University of Waterloo (Canada) and in 2007 Doctor Honoris Causa of the Polytechnic University of Bucharest (Romania). He is "Honorary Member of the Senate" of the AGORA University of Romania since May 2008 He has been Vice President of the SEE (French Society of Electrical and Electronics Engineers) from 2000 to 2006 in charge of the technical committees. He his the director of publication of the SEE electronic Journal e-STA and chair the publication committee of the REE Dr BORNE has been Member of the CNU (French National Council of Universities, in charge of nominations and promotions of French Professors and Associate Professors) 1976-1979, 1992-1999, 2004-2007 He has been Director of the French Group of Research (GDR) of the CNRS in Automatic Control from 2002 to 2005 and of a "plan pluriformations" from 2006 to 2009. Dr BORNE has been member of the Multidisciplinary Assessment Committee of the "Canada Foundation for Innovation" in 2004 and 2009. He has been referee for the nominations of 24 professors in USA and Singapore. He is listed in the "Who is Who in the World" since 1999.

## Plenary Lecture 2

## Applications of Linear Algebra in Signal Processing, Wireless Communications and Bioinformatics

## Professor Erchin Serpedin Department of Electrical and Computer Engineering Texas A&M University USA E-mail: serpedin@ece.tamu.edu

**Abstract:** In this talk, we will review some of the most important applications of linear algebra in signal processing, wireless communications and bioinformatics, and then outline some of the major open problems which might benefit by the usage of linear algebra concepts and tools.

**Brief Biography of the Speaker:** Dr. Erchin Serpedin is currently a professor in the Department of Electrical and Computer Engineering at Texas A&M University in College Station. He is the author of 2 research monographs, 1 textbook, 9 book chapters, 105 journal papers and 175 conference papers. Dr. Serpedin serves currently as associate editor for the Physical Communications Journal (Elsevier) and EURASIP Journal on Advances in Signal Processing, and as Editor-in-Chief of the journal EURASIP Journal on Bioinformatics and Systems Biology edited by Springer. He is an IEEE Fellow and his research interests include signal processing, biomedical engineering, bioinformatics, and machine learning.

## **Plenary Lecture 3**

## **Reliability Life Cycle Management for Engineered Systems**

Professor George Vachtsevanos Professor Emeritus Georgia Institute of Technology USA E-mail: george.vachtsevanos@ece.gatech.edu

**Abstract:** Engineered systems are becoming more complex and by necessity more unreliable resulting in detrimental events for the system itself and its operator. There is evidence to support the contention that industrial and manufacturing processes, transportation and aerospace systems, among many others, are subjected to severe stresses, external and internal, that contribute to increased cost, operator workload, frequent and catastrophic mishaps that require the development and application of new and innovative technologies to improve system reliability, safety, availability and maintainability. These requirements are not true only for strictly engineered systems but are often discussed in business and finance, biological systems and social networks. We introduce in this talk a systematic and verifiable methodology to improve system reliability, reduce operating costs and optimize system design or maintenance practices. The enabling technologies build upon modeling tools to represent critical system functions, a prognostic strategy to predict the long-term behavior of systems under stress, reliability analysis methods exploiting concepts of probabilistic design and an optimization algorithm to arrive at optimum system design for improved reliability. We demonstrate the efficacy of the approach with examples from the engineering domain.

**Brief Biography of the Speaker:** Dr. George Vachtsevanos is currently serving as Professor Emeritus at the Georgia Institute of Technology. He served as Professor of Electrical and Computer Engineering at the Georgia Institute of Technology from 1984 until September, 2007. Dr Vachtsevanos directs at Georgia Tech the Intelligent Control Systems laboratory where faculty and students began research in diagnostics in 1985 with a series of projects in collaboration with Boeing Aerospace Company funded by NASA and aimed at the development of fuzzy logic based algorithms for fault diagnosis and control of major space station subsystems. His work in Unmanned Aerial Vehicles dates back to 1994 with major projects funded by the U.S. Army and DARPA. He has served as the Co-PI for DARPA's Software Enabled Control program over the past six years and directed the development and flight testing of novel fault-tolerant control algorithms for Unmanned Aerial Vehicles. He has represented Georgia Tech at DARPA's HURT program where multiple UAVs performed surveillance, reconnaissance and tracking missions in an urban environment. Under AFOSR sponsorship, the Impact/Georgia Team is developing a biologically-inspired micro aerial vehicle. His research work has been supported over the years by ONR, NSWC, the MURI Integrated Diagnostic program at Georgia Tech, the U,S. Army's Advanced Diagnostic program, General Dynamics, General Motors Corporation, the Academic Consortium for Aging Aircraft program, the U.S. Air Force Space Command, Bell Helicopter, Fairchild Controls, among others. He has published over 300 technical papers and is the recipient of the 2002-2003 Georgia Tech School of ECE Distinguished Professor Award and the 2003-2004 Georgia Institute of Technology Outstanding Interdisciplinary Activities Award. He is the lead author of a book on Intelligent Fault Diagnosis and Prognosis for Engineering Systems published by Wiley in 2006.

## **Plenary Lecture 4**

## Augmented Reality: The Emerging Trend in Education

Professor Minjuan Wang San Diego State University USA E-mail: mwang@mail.sdsu.edu

**Abstract:** Augmented Reality (AR) is the layering of virtual information over the real, 3-D world to produce a blended reality. AR has been considered a significant tool in education for many years. It adds new layers of interactivity, context, and information for learners which can deepen and enrich the learning experience. The combination of real and virtual allows the student to engage in learning about a topic from multiple perspectives and data sources at levels that are not always available in traditional classroom settings and interactions.

As the usage of mobile devices in formal settings continues to rise, so does the opportunity to harness the power of augmented reality (AR) to enhance teaching and learning. Many educators have experimented with AR, but has it proven to improve what students grasp and retain? Is AR just another fun way to engage students, with little transformation of learning? This plenary speaking will introduce augmented reality as an emerging trend in education, provide an overview of its current development, explore examples of curriculum integration, and also suggest approaches for success.

**Brief Biography of the Speaker:** Dr. Minjuan Wang (Professor of San Diego State University; Distinguished Research Professor of Shanghai International Studies University)

Homepage: http://www.tinyurl.com/minjuan

Minjuan is Professor of Learning, Design, and Technology at San Diego State University (California, USA), and distinguished professor of Shanghai International Studies University (Shanghai, China). She was recently selected as the "Oriental Scholar" by the Municipal Educational Committee of Shanghai). In addition, she and her American colleagues obtained a four-year 1.3 million grant to study environment protection (including the Golden monkeys) in Fanjingshan, Guizhou province.

Minjuan's work has been highly interdisciplinary, covering the field of education, technology, computer science, geography, and communication. In her 14 years at SDSU, she teaches Designing and Developing Learning for the Global Audience, Mobile Learning Development, Technologies for Course Delivery, and Methods of Inquiry. Her research specialties focus on online learning, mobile learning, Cloud Learning, and intelligent learning (as part of the Intelligent Camps initiative launched by British Telecom). Minjuan is the Editor-in-Chief of a newly established journal-- EAI Transactions on Future Intelligent Educational Environments. She also serves on the editorial boards for four indexed journals: Open Education Research,

International Journal on E-Learning (IJEL), the Open Education Journal, and Journal of Information Technology Application in Education.

As a winner of several research awards, Minjuan is recognized as one of the high impact authors in blended and mobile learning. She has more than 80 peer-reviewed articles published in indexed journals, such as Educational Technology Research and Development, IEEE Transactions on Education, and British Journal of Educational Technology. She was a keynote and invited speaker to 11 international conferences. In addition, she is also an accomplished creative writer and an amateur flamenco dancer. Her recent Novel--Walking in this Beautiful World—has inspired many young people around the world.

## **Plenary Lecture 5**

## Application of Multivariate Empirical Mode Decomposition in EEG Signals for Subject Independent Affective States Classification

## Prof. Konstantinos N. Plataniotis Department of Electrical and Computer Engineering University of Toronto CANADA E-mail: kostas@ece.utoronto.ca

Abstract: Physiological signals, EEG in particular, are inherently noisy and non-linear in nature which are challenging to work with using conventional linear signal processing methods. In this paper, we are adopting a new signal processing method, Multivariate Empirical Mode Decomposition, as a preprocessing method to reconstruct EEG signals according to its instantaneous frequencies. To test its effectiveness, we applied this signal reconstruction technique to analyze EEG signals for a 2-dimensional affect states classification application. To evaluated the proposed EEG signal processing system, a three-class classification experiment were carried out on the "Emobrain" dataset from eNTERFACE'06 with K-nearest neighbors (KNN) and Linear Discriminate Analysis (LDA) as classifiers. A leave-one-subject out cross validation process were used and an averaged correct classification rate of 90.77% were achieved. Another main contribution of this paper was inspired by the growth of non-medical grade EEG headsets and its potential in advanced human-computer interface design. However, to reduce cost and invasiveness, consumer grade EEG headsets have far less number of electrodes. In this paper, we used emotion recognition as a case study, and applied Genetic Algorithm to systematically select the critical channels (or sensor locations) for this application. The results of this study will shed lights on the sensor configuration challenges faced by most consumer-grade EEG headset design projects.

**Brief Biography of the Speaker:** Konstantinos N. (Kostas) Plataniotis received his B. Eng. degree in Computer Engineering from University of Patras, Greece and his M.S. and Ph.D. degrees in Electrical Engineering from Florida Institute of Technology Melbourne, Florida. He was with the Computer Science Department at Ryerson University, Ontario, Canada from July 1997 to June 1999. Dr. Plataniotis is currently a Professor with The Edward S. Rogers Sr. Department of Electrical and Computer Engineering at the University of Toronto in Toronto, Ontario, Canada, where he directs the Multimedia Laboratory. He is a founding member and the inaugural Director – Research of the Identity, Privacy and Security Institute, IPSI, (www.ipsi.utoronto.ca). Kostas was the Director (January 2010- June 2012) of the Knowledge Media Design Institute, KMDI, (www.kmdi.utoronto.ca) at the University of Toronto.

Dr. Plataniotis was the Guest Editor for the March 2005 IEEE Signal Processing Magazine special issue on "Surveillance Networks and Services", and the Guest Editor for the EURASIP Applied

Signal Processing Journal's special issue on "Advanced Signal Processing & Pattern Recognition Methods for Biometrics". He is a member of the IEEE Periodicals Review and Advisory Committee (2011-2013); he has served as a member of the 2008 IEEE Educational Activities Board; he chaired of the IEEE EAB Continuing Professional Education Committee, and he served as the 2008 representative of the Computational Intelligence Society to the IEEE Biometrics Council. Dr. Plataniotis chaired the 2009 Examination Committee for the IEEE Certified Biometrics Professional (CBP) Program (www.ieeebiometricscertification.org) and he served on the Nominations Committee for the IEEE Council on Biometrics. He was a member of the Steering Committee for the IEEE Transaction on Mobile Computing, an Associate Editor for the IEEE Signal Processing Letters as well as the IEEE Transactions on Neural Networks and Adaptive Systems and he has served as the Editor-in-Chief for the IEEE Signal Processing Letters from January 1, 2009 to December 31, 2011. Dr. Plataniotis chaired the IEEE Toronto Signal Processing and Applications Toronto Chapter from 2000 to 2002, he was the 2004-05 Chair of the IEEE Toronto Section and a member of the 2006 as well as 2007 IEEE Admissions & Advancement Committees. He served as the Technical Program Committee Co-Chair for the 2013 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP 2013) and he is the Vice President – Membership for the IEEE Signal Processing Society (2014-2016). Dr. Plataniotis is a Fellow of IEEE, Fellow of the Engineering Institute of Canada, a registered

Dr. Plataniotis is a Fellow of IEEE, Fellow of the Engineering Institute of Canada, a registered professional engineer in the province of Ontario, and a member of the Technical Chamber of Greece.

The recipient of numerous grants and research contracts as the principal investigator, he speaks internationally and writes extensively in his field and he has been a consultant to a number of companies. He has served as lecturer in 12 short courses to industry and continuing education programs; he is a contributor to seventeen books, the co-author of "Color Image Processing and Applications", Springer Verlag, 2000, (ISBN-3-540-66953-1) and "WLAN Positioning Systems: Principles & applications in Location-based Services", Cambridge University Press, 2012 (ISBN 978-0-521-9185-2), "Multi-linear Subspace Learning: Reduction of multi-dimensional data}, CRC Press, 2013, (ISBN: 978-14398557243). He is the co-editor of "Color Imaging: Methods and Applications", CRC Press, September 2006, (ISBN 084939774X) and the Guest Editor of the IEEE/Wiley Press volume on "Biometrics: Theory, Methods and Applications" published in October 2009 (ISBN: 9780470247822). Dr. Plataniotis has published more than 400 papers in refereed journals and conference proceedings. In 2005 he became the recipient of the IEEE Canada Engineering Educator Award for "contributions to engineering education and inspirational guidance of graduate students". Dr. Plataniotis is the joint recipient of the "2006 IEEE Trans. on Neural Networks Outstanding Paper Award" for the published in 2003 "Face recognition using kernel direct discriminant analysis algorithms", IEEE Trans. on Neural Networks, Vol. 14, No 1, 2003.

## **Plenary Lecture 6**

## State of the Art and Recent Progress in Uncertainty Quantification for Electronic Systems (i.e. Variation-Aware or Stochastic Simulation)

Professor Luca Daniel Electrical Engin. & Computer Science Massachusetts Institute of Technology (MIT) Cambridge, MA, USA E-mail: luca@mit.edu

**Abstract:** On-chip and off chip fabrication process variations have become a major concern in today's electronic systems design since they can significantly degrade systems' performance. Existing commercial circuit and MEMS simulators mostly rely on the well known Monte Carlo algorithm in order to predict and quantify such performance degradation. However during the last decade a large variety of more sophisticated and efficient alternative approaches have been proposed to accelerate such critical task. This talk will first review the state of the art of most modern uncertainty quantification techniques including intrusive and sampling-based ones. It will be shown in particular how parameterized model order reduction, and low-rank tensor based representations can be used to accelerate most uncertainty quantification tools and to handle the curse of dimensionality. Examples will be presented including amplifiers, mixers, voltage controlled oscillators with tunable micro-electro-mechanical capacitors and phase locked loops.

**Brief Biography of the Speaker:** Luca Daniel is an Associate Professor in the Electrical Engineering and Computer Science Department of the Massachusetts Institute of Technology (MIT). Prof. Daniel received the Ph.D. degree in Electrical Engineering from the University of California, Berkeley, in 2003. In 1998, he was with HP Research Labs, Palo Alto. In 2001, he was with Cadence Berkeley Labs.

Dr. Daniel research interests include development of integral equation solvers for very large complex systems, stochastic field solvers for large number of uncertainties, and automatic generation of parameterized stable compact models for linear and nonlinear dynamical systems. Applications of interest include simulation, modeling and optimization for mixed-signal/RF/mm-wave circuits, power electronics, MEMs, nanotechnologies, materials, MRI, and the human cardiovascular system.

Prof. Daniel has received the 1999 IEEE Trans. on Power Electronics best paper award; the 2003 best PhD thesis awards from both the Electrical Engineering and the Applied Math departments at UC Berkeley; the 2003 ACM Outstanding Ph.D. Dissertation Award in Electronic Design Automation; 5 best paper awards in international conferences, 8 additional nominations for best paper award; the 2009 IBM Corporation Faculty Award; and the 2010 IEEE Early Career Award in Electronic Design Automation.

Recent Advances in Circuits

## Distributed power generation using small wind turbine systems: new chaotic attractor in back-to-back converter dynamics

Donato Cafagna and Giuseppe Grassi

Abstract—Referring to distributed power generation, this paper deals with a small wind turbine system (WTS) constituted by a permanent magnet synchronous generator (PMSG) connected to the grid via a back-to-back converter. By considering the behavior of a grid-side converter in the presence of voltage sags, the study shows that a new chaotic attractor is generated when the size of the dc-link capacitor is reduced. The reported time waveforms and state-space attractor clearly highlight that the system becomes chaotic during the voltage sag, being stable before and after the occurrence of the disturbance. Finally, the chaotic behavior is validated via the computation of the maximum Lyapunov exponent, thus confirming the novel phenomenon described herein.

*Keywords*—Chaotic attractors, converters back-to-back, Lyapunov exponents, nonlinear dynamics, wind turbine systems.

#### I. INTRODUCTION

N the field of renewable energy, great efforts have been recently devoted to distributed generation through small wind turbine systems (WTSs). This choice is motivated by virtue of their higher feed-in tariffs, capability to work in island-mode for isolated communities, national laws imposing simpler grid connection, lower noise level and lower impact on the landscape [1-3]. Over the last years the field of small generation has been mainly dominated by the use of asynchronous generators directly connected to the grid. Very recently, WTSs based on permanent magnet synchronous generators (PMSGs) and back-toback converters have been introduced [4-5]. The back-toback converter consists of a PWM (Pulse Width Modulation) rectifier and a PWM inverter connected with a common dc-link. The presence of a fast control loop for the dc-link voltage makes perceive the possibility of reducing the size of the dc-link capacitor, seemingly without affecting the inverter performance [6]. However, since back-to-back converters are rich in nonlinearities, it is important to carefully study their dynamics. Namely, chaotic behaviors may occur in nonlinear dynamical systems, especially in the presence of disturbances [7].

Note that the large increase in the installed wind capacity necessitates that WTSs remain in operation in the case of the grid disturbances.

Based on these considerations, in this paper the nonlinear dynamics of a grid-side converter is analyzed by reducing the size of the dc-link capacitor in the presence of voltage sags. The conducted analysis shows that a new chaotic attractor is generated for some values of the dc-link capacitance. In particular, the paper reports the time waveforms of the voltage across the capacitor and the grid current in the *d*-axis, showing that chaotic behaviors occur during the voltage sag. Moreover, in order to carefully analyze the conceived phenomena, some attractors are plotted in the state space. These attractors clearly highlight that the system becomes chaotic during the voltage sag, being stable before and after the occurrence of the disturbance. To the best of our knowledge, the results reported herein represent a new finding in the field of small WTSs constituted by PMSGs connected to the grid via back-to-back converters.

The paper is organized as follows. In Section II the overall system and the grid side converter control are described. Section III presents the basic notions on chaos theory, whereas in Section IV chaotic phenomena occurring during voltage sags are analyzed in detail. Finally, the chaotic behavior of the considered small WTS is validated via the computation of the Lyapunov exponents.

#### II. WIND TURBINE SYSTEM AND GRID-SIDE CONVERTER

In small WTS (power unit less than 200 kW) two main choices are available: variable speed asynchronous generators and synchronous generators. Referring to variable speed asynchronous generators, they can easily operate in parallel with large power systems (the utility grid controls voltage and frequency whereas static and reactive compensating capacitors are used for power factor correction and harmonic reduction). On the other hand, over the last years the most common solution for wind generator is based on PMSG directly connected to the turbine [6]. This solution is particularly advantageous as it reduces the frequency and the costs of maintenance operations. In fact these generators are self-excited, allowing operation at high power factor and high efficiency. Moreover multipolar PMSG does not need the gearbox to adapt the rotor speed to the blade speed. This advantage becomes crucial for wind turbine installation in

D. Cafagna is with the Department of Engineering for Innovation, University of Salento, 73100 Lecce - ITALY (e-mail: donato.cafagna@unisalento.it).

G. Grassi is with the Department of Engineering for Innovation, University of Salento, 73100 Lecce - ITALY (e-mail: giuseppe.grassi@unisalento.it).

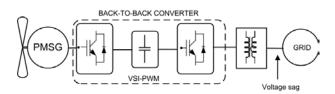

harsh environment characterized by low temperature [2]. Figure 1 shows the scheme of a small WTS based on a PMSG.

Fig. 1: Wind Turbine System.

The considered PMSG is connected to the grid through a bidirectional converter. It consists of two VSI (Voltage Source Inverter)-PWM converters connected by a storage capacitor: the converter connected to the generator is used as a rectifier, while the converter connected to the grid is used as an inverter. To achieve full control of the output, the dc-link voltage must be boosted to a level higher than the amplitude of the grid voltage [2]. The power flow of the grid side converter is controlled in order to keep the dc-link voltage constant, while the control of the generator side is set to suit the magnetization demand and the reference speed or torque.

A technical advantage of this topology is the capacitor decoupling between the grid converter and the generator converter. This decoupling offers separate control of the two converters, allowing compensation of asymmetry both on the generator side and on the grid side, independently [1]-[3]. Based on the decoupling capability, this paper focuses on the grid side control of the converter, given that the voltage sags occur at the grid side (especially when connected to weak power grids).

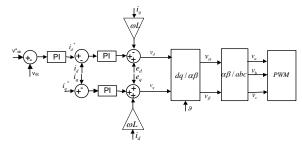

Referring to the control scheme of the grid-side converter, its block diagram is shown in Fig. 2. The converter is controlled by two cascade-loops: the outer dcvoltage loop provides the reference for the inner current loop. In particular, the grid-side converter is controlled with a voltage-oriented control (VOC) based on the coordinate transformation between the stationary  $\alpha$ - $\beta$  and the synchronous *d*-*q* reference frames. This control strategy guarantees fast transient response and high static performance due to the internal control loops [8].

Fig. 2: Grid-side converter control.

The decomposition of the grid current in two axes provides a decoupled control for the active and reactive power and it allows to obtain an high power factor and sinusoidal grid currents [8]-[11]. The active power P and the reactive power Q produced by WTS are:

$$P = \frac{3}{2} \left( e_d i_d + e_q i_q \right), \qquad Q = \frac{3}{2} \left( e_q i_d - e_d i_q \right)$$

(1)

If the *dq*-frame has the *d*-axis perfectly aligned on the grid voltage vector, it results  $e_q = 0$  and *P* and *Q* become proportional to  $i_d$  and  $i_q$ , respectively:

$$P = \frac{3}{2} e_d i_d, \quad Q = -\frac{3}{2} e_d i_q$$

(2)

indicating that the reactive power flow is controlled via  $i_q$  and the dc-link is controlled via  $i_d$ . The reference current in the *q*-axis of the current loop is usually set to zero in order to achieve zero phase angle between voltage and current and so unity power factor can be achieved [8]. The grid side converter control is given by:

The grid-side converter control is given by:

$$\begin{cases} v_d^* = v_d + \omega L_{tot} \cdot i_q - e_d \\ v_q^* = v_q - \omega L_{tot} \cdot i_d - e_q \end{cases}$$

(3)

The choice of  $v_d^*$  and  $v_q^*$  as control variables instead of  $v_d$  and  $v_q$  lead to decoupling of the dynamics of the *d* and *q* axes. As a consequence the plant of the system is:

$$\begin{cases} \dot{i}_{d} = \frac{v_{d}^{*}}{L_{tot}s + R_{tot}} \\ \dot{i}_{q} = \frac{v_{q}^{*}}{L_{tot}s + R_{tot}} \end{cases}$$

(4)

The PI controllers have been tuned with the technical optimum design method. The parameters  $k_p$  and  $T_i$  are

$$k_{p} = \frac{L_{tot}}{3T_{s}}, \quad T_{I} = \frac{L_{tot}}{R_{tot}}$$

(5)

where  $T_s$  is the sampling time [2].

#### III. CHAOS THEORY FUNDAMENTALS

Chaos theory deals with the study of complex behaviors in deterministic nonlinear systems [12]-[16]. In particular, a nonlinear dynamical system is considered to be chaotic if the following three properties hold:

- 1) sensitive dependence to initial conditions;

- 2) topological mixing;

- 3) density of periodic orbits.

Sensitive dependence to initial conditions means that small differences between two sets of initial conditions yield diverging trajectories, rendering long-term prediction impossible to be carried out (an effect usually named "butterfly effect") [12]. Note that such behavior occurs even though the considered systems are deterministic and no stochastic phenomena are involved.

*Topological mixing* means that the system will evolve over time so that any given region or open set of its phase space will eventually overlap with any other given region. *Density of periodic orbits* means that every point in the space is approached arbitrarily closely by periodic orbits [12]. Based on these properties, the trajectories of a chaotic system present the following features [15]:

- 1) they are not periodic;

- 2) they are bounded;

- 3) they cannot be reproduced;

- 4) they do not intersect each other.

From a practical point of view, a chaotic solution can be identified with a bounded steady-state behavior that is *not* an equilibrium point, *not* periodic, and *not* quasiperiodic. Referring to the time waveform representation, chaotic trajectories behave in a *random-like* fashion. On the other hand, referring to the state-space representation, the complicated geometrical object to which the chaotic trajectories are attracted is called *chaotic attractor* [15].

A key issue in chaos theory is to determine whether the nonlinear dynamical system under consideration is chaotic or non-chaotic. To this purpose, one approach consists in estimating the largest Lyapunov exponent (i.e., a generalization of the eigenvalues at an equilibrium point) from time series data [15]. Since a positive Lyapunov exponent indicates diverging trajectories, what distinguishes chaotic behaviors from non-chaotic ones is the existence of a positive Lyapunov exponent.

#### IV. NEW CHAOTIC ATTRACTOR IN BACK-TO-BACK CONVERTER DYNAMICS

It is well known that, due to the non-smooth operation of power electronic converters, back-to-back converters are rich in nonlinearities [7]. As a consequence, it is important to study the nonlinear dynamic behavior of the proposed system, especially in the presence of voltage sags. Based on these considerations, in this Section the nonlinear dynamics of the grid-side converter are analyzed, with the aim to check the existence of some operating conditions for which the system is chaotic. In particular, deep investigation has been devoted to the system configuration in which the capacitance is made small enough, thus allowing the replacement of the commonly used electrolytic capacitors with plastic film capacitors.

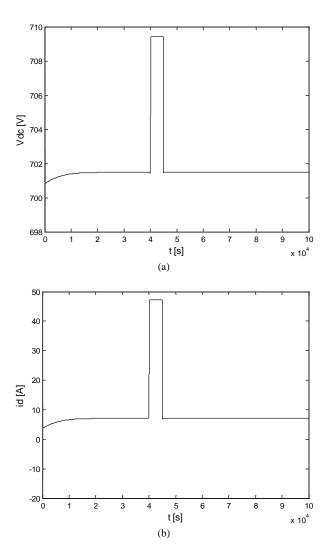

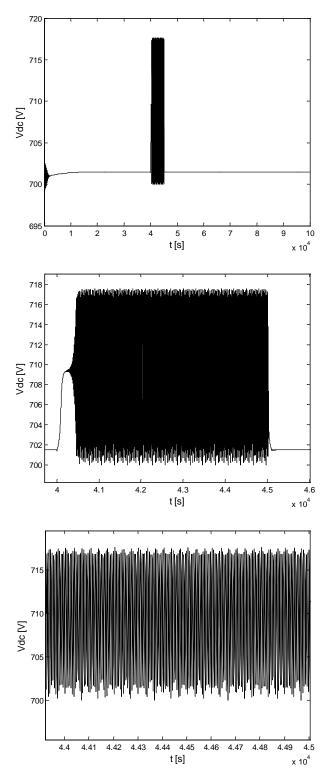

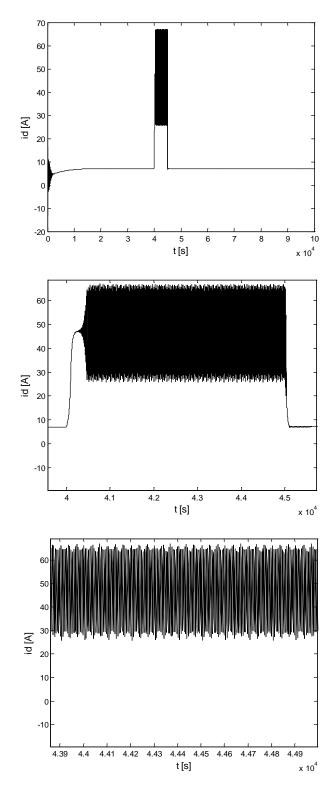

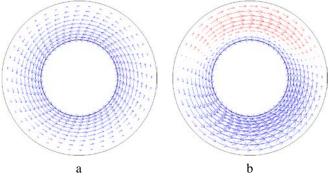

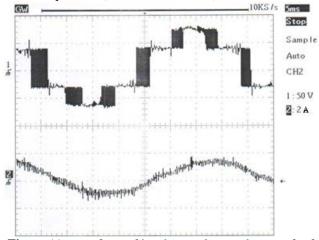

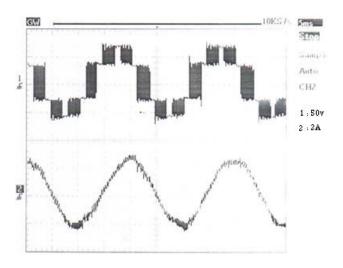

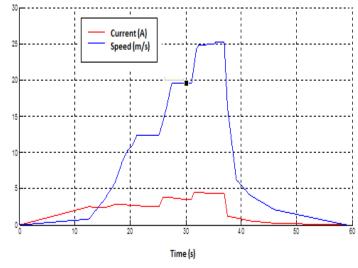

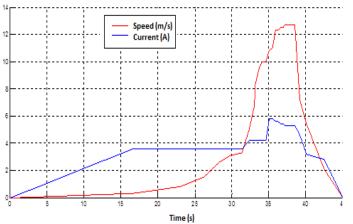

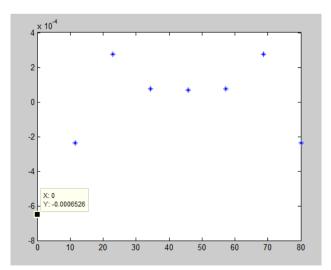

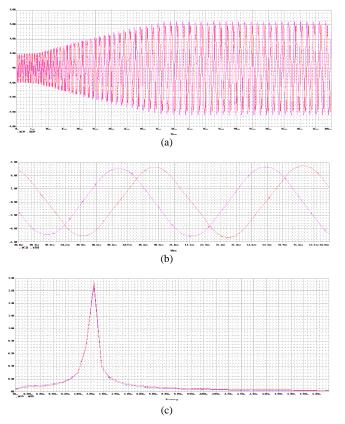

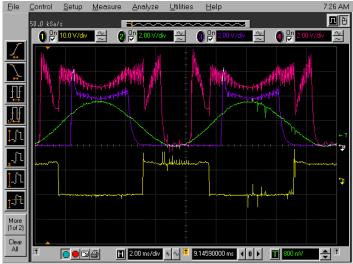

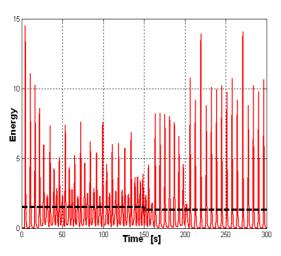

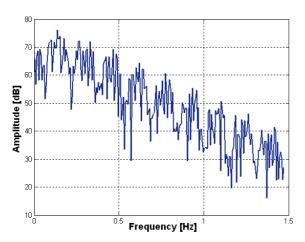

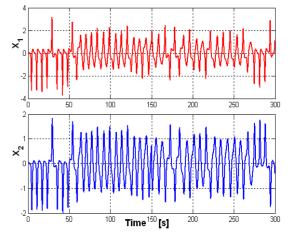

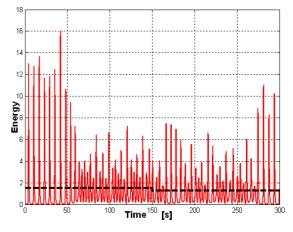

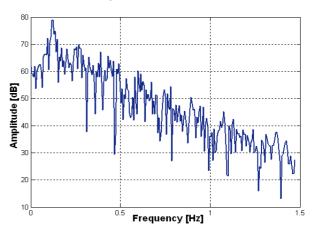

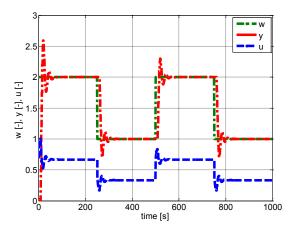

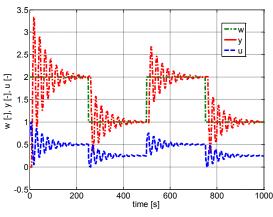

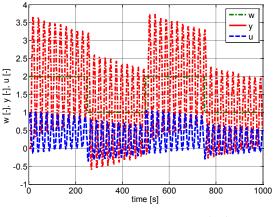

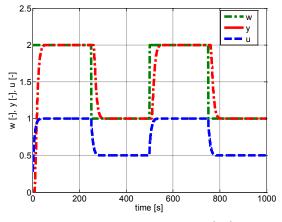

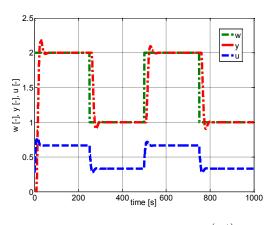

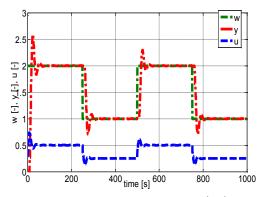

Referring to the block diagram reported in Fig.1, a voltage sag is considered at the grid side, which starts at t = 4s with a duration of 0.5s. Owning to the voltage sag, the final voltage is reduced to the 85% of the initial voltage (see Appendix for Low Voltage Ride Through requirements). When the nominal value  $C = 500 \mu F$  is considered, the system behaves according to the design specifications as shown in Fig.3, which plots the time waveforms of the voltage  $V_{dc}$  across the capacitor (Fig.3 (a)) and the current  $i_d$  (Fig.3 (b)). Successively, the system is analyzed by reducing the value of the capacitance. When the value  $C = 280 \mu F$  is reached, an interesting nonlinear behavior is found during the voltage sag, that is, the voltage  $V_{dc}$  across the capacitor behaves chaotically. Such behavior is clearly shown in Fig.4, which plots the time waveforms of the voltage  $V_{\rm dc}$  for different time resolutions.

Fig. 3 Time waveforms: (a) voltage  $V_{dc}$  across the capacitor; (b) current  $i_d$  for  $C = 500 \mu$ F.

Notice that the time waveforms of  $V_{dc}$  are bounded and not periodic, i.e., they behave in a *random-like* fashion. The same chaotic behavior is found for the current  $i_d$ during the voltage sag (see Fig.5).

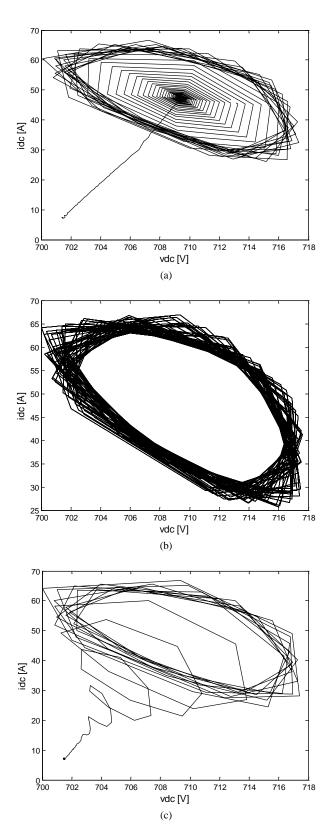

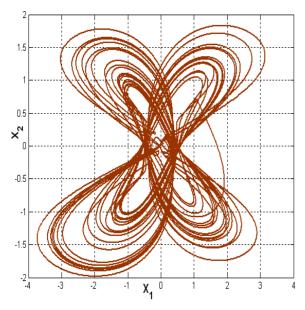

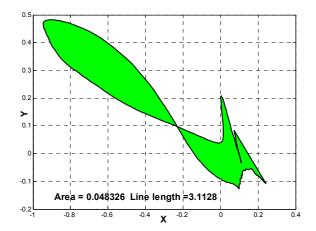

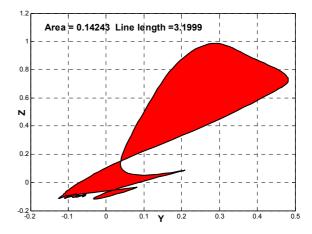

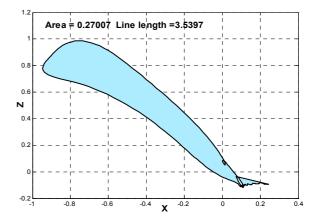

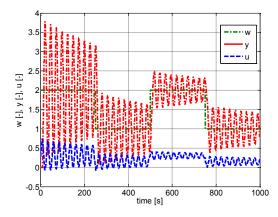

By plotting the variables  $V_{dc}$  and  $i_d$  in the state-space, the chaotic attractor depicted in Fig.6 is obtained. In particular, Fig.6(a) shows that the system trajectories start from the initial stable state (701.5V, 7.1A) that exists before the occurrence of the voltage sag. Then the system trajectories approach the one-scroll chaotic attractor reported in Fig.6(b). When the voltage sag ends, the system trajectories return to the initial stable equilibrium point (Fig.6(c)).

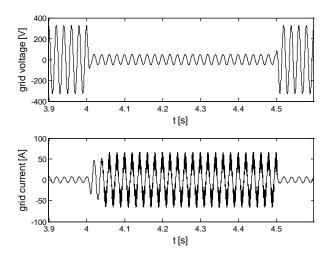

Referring to the grid voltage, its dynamic behavior is reported in Fig.7 (upper subplot). Note that the sinusoidal behavior is preserved during the voltage sag, even though the voltage amplitude reduces to the 85% of the initial value. On the other hand, the amplitude of the grid current increases during the voltage sag, as shown in Fig.7 (lower subplot). Recent Advances in Circuits

Fig. 4 Time waveforms of the voltage  $V_{dc}$  for different time resolutions ( $C = 280 \mu$ F).

Fig. 5 Time waveforms of the current  $i_d$  for different time resolutions ( $C = 280 \mu$ F).

Fig. 6 Plots in the state-space ( $V_{dc}$ ,  $i_d$ ) for  $C = 280\mu$ F: (a) the trajectories leave the initial stable state (701.5V, 7.1A) that exists before the occurrence of the voltage sag; (b) the trajectories describe a one-scroll chaotic attractor; (c) the trajectories return to the initial stable equilibrium point when the voltage sag ends.

Fig. 7 Time waveforms of the grid voltage and the grid current during the voltage sag ( $C = 280 \mu$ F).

In order to verify if the proposed small WTS behaves chaotically for  $C = 280\mu$ F, the maximum Lyapunov exponent has been computed by considering the time series data obtained during the voltage sag. Since the obtained maximum Lyapunov exponent is positive (i.e.,  $\lambda_{max} = 1.69$ ), it can be concluded that the attractor reported in Fig.6(b) is truly chaotic.

#### V. CONCLUSIONS

The chaotic phenomena occurring during the voltage sag, as described through the paper, represent a new finding for small WTSs constituted by a PMSG connected to the grid via back-to-back converters. In particular, this paper has analyzed the nonlinear dynamics of the grid-side converter in the presence of voltage sags. The study has shown that a new chaotic attractor is generated during the voltage sag when the size of the dc-link capacitor is reduced, being the system stable before and after the occurrence of the disturbance. The chaotic behavior of the considered small WTS has been validated via the computation of maximum Lyapunov exponent.

#### APPENDIX

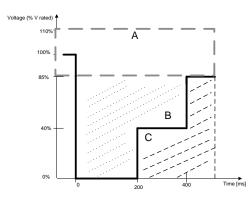

The large increase in the installed wind capacity necessitates that WTS remains in operation in the case of the grid disturbances. For this reason grid codes issued during the last years demand that WTSs must withstand voltage sag to a certain percentage of the nominal voltage and for a specified duration. Such requirements are known as Low Voltage Ride Through (LVRT) [17]. The Italian grid code CEI 0-21 requests that WTS with rated power  $\geq$  6 kVA must be able not to disconnect instantly during a voltage sag but it must be able to fulfill the LVRT requirements [18]. When the voltage sag occurs, if the WTS is in the region B the WTS shall remain connected to the grid and the active and reactive power injected into the grid can be set to zero. When V  $\geq$  85% V<sub>rated</sub> (region A) the

system is in normal condition and takes  $t \le 200$ ms to inject into the grid  $P = P_{rated}$  and  $Q = Q_{rated}$ . In the region C it is possible the disconnection of the system from the grid [18].

Fig. 8 LVRT requirements.

#### REFERENCES

- F. Blaabjerg, Zhe Chen, S.B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Transactions on Power Electronics*, vol.19, no.5, pp. 1184-1194, Sept. 2004.

- [2] Zhe Chen, J. M. Guerrero, F. Blaabjerg, "A Review of the State of the Art of Power Electronics for Wind Turbines," *IEEE Transactions on Power Electronics*, vol.24, no.8, pp. 1859-1875, August 2009.

- [3] Onder Ozgener, "A small wind turbine system (SWTS) application and its performance analysis," *Energy Conversion and Management* 47, 2006, pp.1326-1337.

- [4] M.Godoy Simoes, S. Chakraborty, R.Wood, "Induction Generators for Small Wind Energy," *IEEE Power Electronics Society Newsletter*, pp.19-23, Third Quarter 2006.

- [5] I. Boldea, "Variable speed generator" Taylor & Francis Group, Boca Raton 2006.

- [6] J. Wang, D. Xu, B. Wu, Z. Luo, "A Low-Cost Rectifier Topology for Variable-Speed High-Power PMSG Wind Turbines," *IEEE Transactions on Power Electronics*, vol.26, no.8, pp.2192-2200, August 2011.

- [7] S. Banerjee and G.C. Verghese, (Editors) "Nonlinear Phenomena in Power Electronics: Attractors, Bifurcations, Chaos, and Nonlinear Control," Wiley-IEEE Press, 2001.

- [8] R.Teodorescu, M. Liserre, P. Rodriguez, "Grid Converters for photovoltaic and Wind Power Systems," second edition Wiley, 2011.

- [9] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galván, R. C. P. Guisado, Á M Prats, J I. León, and N. Moreno-Alfonso, "Power-Electronic Systems for the Grid Integration of Renewable Energy Sources: A Survey," *IEEE Transactions on Industrial Electronics*, vol. 53, no. 4, August 2006.

- [10] H. Kömürgügil, Ösman Kükrer, "A New Control Strategy for Single-Phase Shunt Active Power Filters Using a Lyapunov Function," *IEEE Transactions on Industrial Electronics*, vol.53, no.1,Feb. 2006, pp.305-312.

- [11] M. E. Ortúzar, Rodrigo E. Carmi, Juan W. Dixon, Luis Morán, "Voltage-Source Active Power Filter Based on Multilevel Converter and Ultracapacitor DC Link," *IEEE Transactions on Industrial Electronics*, vol.53, no.2, April 2006, pp. 477-485.

- [12] E.Ott, "Chaos in Dynamical Systems," Cambridge University Press, NewYork, 2002.

- [13] D. Cafagna and G. Grassi, "Experimental study of dynamic behaviors and routes to chaos in DC-DC boost converters," *Chaos, Solitons & Fractals*, vol.25, no.2, pp.499-507, 2005.

- [14] D. Cafagna and G. Grassi, "Bifurcation analysis and chaotic behavior in boost converters: experimental results," *Nonlinear Dynamics*, Vol.44, No.1-4, pp.251-262, 2006.

- [15] T. S. Parker and L.O. Chua, "Practical numerical algorithms for chaotic systems," Springer-Verlag, New York, 1989.

- [16] D. Cafagna and G. Grassi, "An effective method for detecting chaos in fractional-order systems," *Int. Journal of Bifurcation and Chaos*, vol.20, no.3, pp.669-678, 2010.

- [17] Rajveer Mittal, K.S. Sandhu, D.K. Jain, "Low Voltage Ride Trough (LVRT) of grid interface wind driven PMSG," *ARPN Journal of Engineering and Applied Sciences*, Vol. 4 no. 5 July 2009, pp. 73-83.

- [18] CEI 0-21 "Reference technical rules for the connection of active and passive users to the LV electrical Utilities, 2011-2012.

## High-Impedance Electrode Contact Monitoring

M. J. Burke, C. Molloy, and H. Fossan

Abstract—The circuit reported in this paper is used to measure the quality of contact of un-gelled ECG electrodes with the human skin in a heart rate monitor used with mothers prior to and during childbirth. The circuit measures the contact impedance continually and gives an indication of whether the impedance is above or below an acceptable threshold. The output of the circuit is then used to give a visual indication that the mother is adequately connected to the heart-rate monitor for the purposes of obtaining reliable measurements of her heart rate. The output signal obtained is then used to interface with an ultrasonic heart rate transducer being used to measure the unborn infant's heart-rate. This provides a method of ensuring that the ultrasound monitor is actually measuring the infant's heart rate rather than that of the mother. The circuit developed measures the quality of contact of stainless-steel electrodes having contact impedance as high as  $100k\Omega$ . It uses an injected signal at a frequency of 5 kHz and can assess the contact of individual left and right electrodes independently.

*Keywords*—Electrode impedance, un-gelled electrodes, heart rate monitoring, ECG amplifier.

#### I. INTRODUCTION

THE Safer Births Program [1], sponsored by the Norwegian Research Council as part of a larger World Health Organization initiative [2], is an action plan aimed at eliminating preventable deaths of infants at birth, with particular focus on developing countries. Many maternity units in these locations are understaffed and in some cases rely on midwives and nurses alone to contend with the complications that arise around birth, without proper access to the advanced medical assistance or equipment needed to deal with them. Few places have sufficient equipment for fetal monitoring such that fetuses in distress are left unattended, adding to the burden of birth asphyxia and stillbirth. Many of the infants born may not be breathing correctly or at all and have pulses which are difficult and sometimes impossible to detect manually. On occasions these infants can be misclassified as stillborn when, in fact, their hearts have not stopped functioning and they could be resuscitated with the help of suitable equipment. Laerdal Medical AS, a Norwegian company that manufactures medical training equipment, is currently extending its range of products to include resuscitation equipment for the scenarios described above. One such product is the Moyo unit shown in Fig 1. This unit is a fetal heart rate monitor which uses an ultrasonic transducer placed on the mother's abdomen to detect the infant's heart beat and indicates the fetal heart rate on a LCD display. One common problem with ultrasonic heart rate monitors is that when the infant's heart beat is difficult to detect the transducer often picks up the mother's heart rate in error [3]. In order to overcome this problem the Moyo unit incorporates an ECG amplifier and circuitry which can be used to measure the mother's heart rate by way of her ECG and to indicate this on a separate LCD display. The Moyo unit is held by the mother giving birth and, when requested to do so, she presses her fingers onto the stainless steel electrodes of the unit which are used to detect her ECG and from this the device measures and displays her heart rate. The values of the two heart rates can then be compared by the midwife and used to discern whether or not the ultrasonic transducer is actually measuring the infant's heart rate reliably or the mother's heart rate in error. To this end it was decided to implement a mechanism in the Moyo unit which would verify that the mother's ECG was being measured reliably by the stainless steel un-gelled electrodes. This is done by measuring the contact impedance of the skin-electrode interface at both electrodes of the Mojo unit and detecting when the mother has pressed her fingers onto the electrodes. The circuit reported in this paper measures the contact impedance of each electrode independently and indicates when the state of contact of either electrode is unsatisfactory for the purposes of reliable ECG measurement, generating a visual alarm under this condition.

Fig. 1. The Handheld Moyo Unit

This work was supported in part by the Norwegian Research Council Grant No. ES506110 under the Safer Births Program.

M. J. Burke is with the Department of Electronic & Electrical Engineering, Trinity College, Dublin 2, Rep. of Ireland. (corresponding author, phone: +353-1-8961740; fax: +353-1-6772442; e-mail: mburke@tcd.ie).

C. Molloy is with the Department of Electronic & Electrical Engineering, Trinity College, Dublin 2, Rep. of Ireland. (e-mail: comolloy@tcd.ie).

H. Fossan is with Laerdal Medical AS. P.O Box 337, Tanke Svilandsgate 30, N-4002 Stavanger, Norway. (e-mail: helge.fossan@laerdal.no).

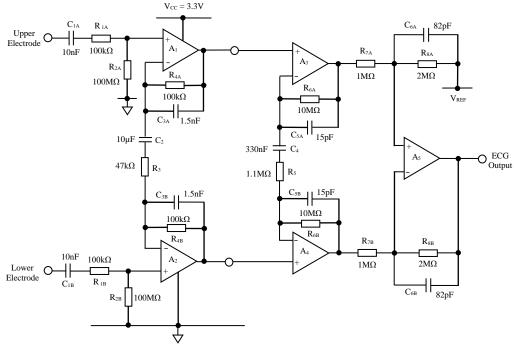

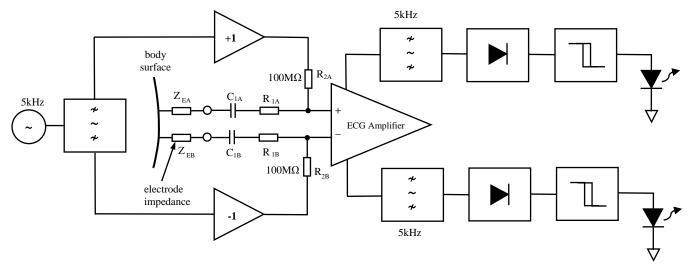

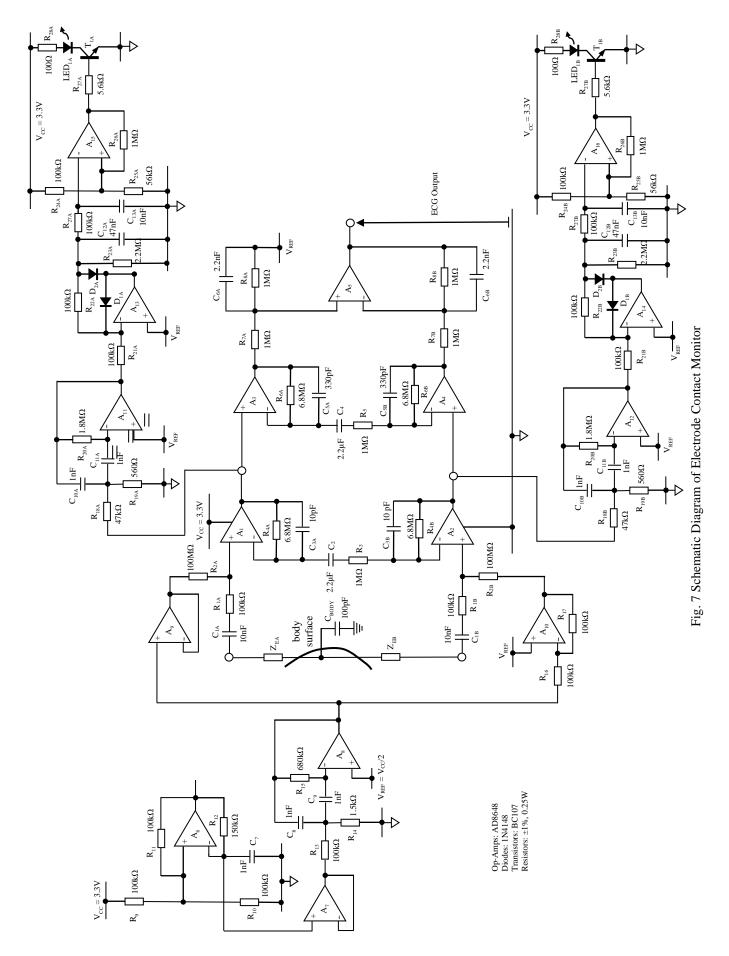

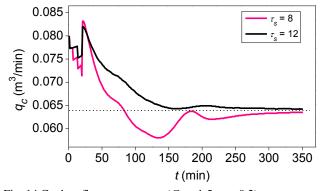

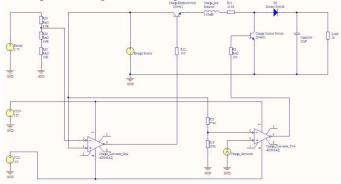

Fig. 2 Schematic Diagram of Existing ECG Amplifier

#### II. BACKGROUND

#### A. Existing ECG Amplifier

The schematic diagram of the front-end ECG amplifier currently in use in the Moyo unit is shown in Fig. 2. This is a three-stage instrumentation ECG amplifier adapted from an earlier design by Burke & Gleeson [4,5] and later improved by Assambo & Burke [6-9]. The 46 dB of differential gain is split primarily between the first stage with 14.4 dB and the second stage with 25.6 dB while the third stage provides 6dB of the gain with differential-to-single-ended conversion. The input stage provides a high differential-mode and common-mode impedance of  $100M\Omega$  in order to preserve adequate commonmode-rejection-ratio (CMRR) when interfacing with highimpedance dry electrodes. The amplifier operates from a single 3.3V supply rail and the input stages are biased to a mid-rail voltage of 1.65V using a separate dc-to-dc convertor chip not shown in the schematic. The ESD protection elements are also omitted for clarity.

#### B. Electrodes

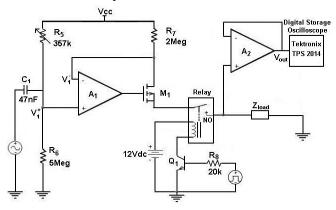

The electrodes used in the Moyo unit shown in Fig. 1 are made of stainless steel with either a polished or a matt surface, as these can easily be disinfected before use with an alcohol wipe. Electrical contact is made with the electrodes by the mother gripping the unit in both hands with her fingers placed on the electrode surfaces as shown. Only the firmness of the mother's grip determines the contact pressure. In order to obtain an indication of the contact impedance of these electrodes a method formerly reported by Baba & Burke [10, 11] was used to characterize the electrodes. The current source shown in Fig. 3 was used to inject a minute current of  $2\mu$ A through the electrodes while being held by the user. The

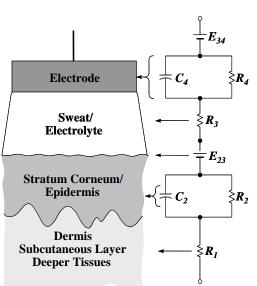

current was activated and then deactivated via the relay for stable periods of 20 - 50s. A 10 kHz sinewave signal was also used to allow the high frequency purely resistive components to be evaluated. A program in MATLAB (MathWorks Inc.) was then used to fit a two time constant C-R model shown in Fig. 4 to the recorded voltage waveforms and to determine the values of the individual components of the model.

Fig. 3 Electrode Impedance Measurement Circuit

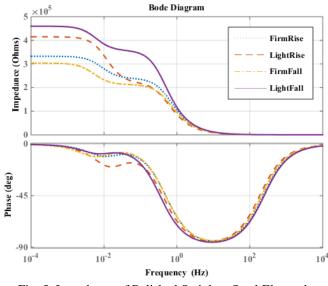

This was done for measurements made on a small number of subjects to get an initial idea of the scale and variation of electrode impedance to be expected. Only the passive components of the model were of interest in this instance and the dc polarization potentials were not measured. The ranges of values measured for each component of the model are listed in Table.1 below. Plots of the magnitude and phase as functions of frequency of a stainless steel electrode having a polished surface are shown in Fig. 5. Plots are shown for light and firm grips of the mother's fingers and for rise and fall phases of the injected current.

| Element        | Minimum | Maximum | Unit |

|----------------|---------|---------|------|

| $R_1 + R_3$    | 2.0     | 5.0     | kΩ   |

| R <sub>2</sub> | 23.2    | 267     | kΩ   |

| C <sub>2</sub> | 1.60    | 878     | μF   |

| R4             | 36.0    | 380     | kΩ   |

| $C_4$          | 0.47    | 55.5    | μF   |

| $	au_2$        | 0.26    | 58.8    | S    |

| $\tau_4$       | 0.13    | 8.62    | S    |

Table 1. Range of Values for the Electrode Model Elements

Fig. 4. An Equivalent Electrical Model of the ECG Electrode

It can be seen that the impedance varies considerably within the frequency range of the ECG signal. The magnitude falls off abruptly before 1 Hz and the phase falls off above 10 Hz. It can be seen that the magnitude of the impedance is less than 10 k $\Omega$  at frequencies above approximately 10 Hz. This is considerably lower than the input common-mode resistance of the amplifier or the protection resistor, R<sub>1</sub>. This indicates that the signal levels involved in measuring the contact impedance of such electrodes are likely to be quite low.

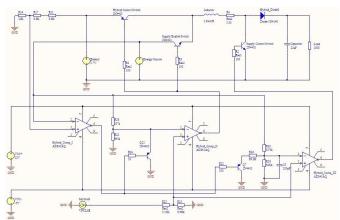

#### C. Measurement System

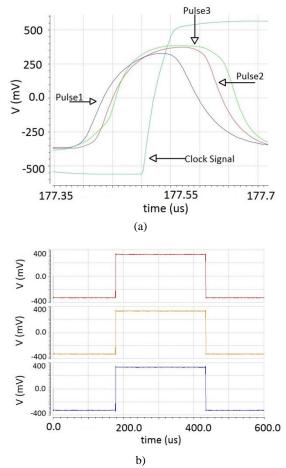

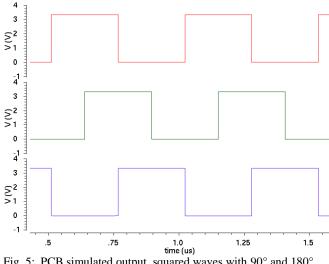

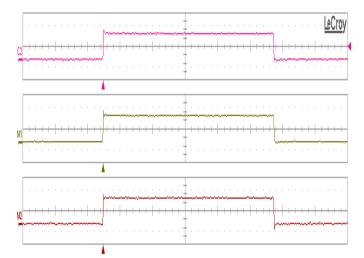

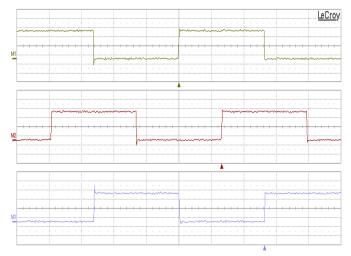

A block diagram of the electrode contact monitoring system and its placement in relation to the ECG amplifier is shown in Fig. 6. An oscillator and filter are used to provide a sinusoidal source signal at a frequency of 5 kHz with an amplitude of 1.5 V peak. Normally one would like the frequency of contact measurement to be much higher than the bandwidth of the ECG signal. However, the parasitic input capacitance of operational amplifiers causes a significant shunting effect at higher frequencies so the value of 5kHz was chosen to avoid this, while at the same time keeping the measurement frequency at least a decade above the ECG band. The sinewave is then buffered in both an inverting and a noninverting amplifier to provide antiphase source signals. These signals are then fed through the common-mode input resistors of the ECG amplifier  $R_{2A}$  and  $R_{2B}$  to the electrode impedances

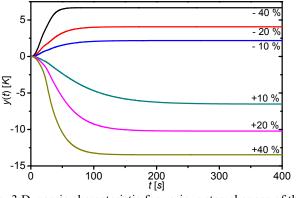

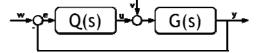

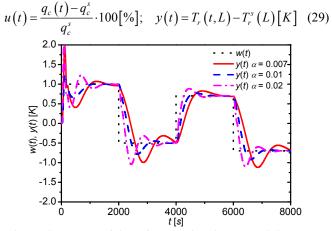

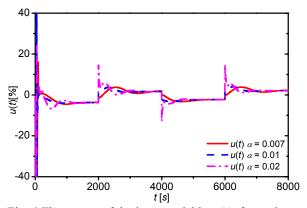

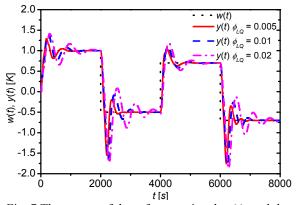

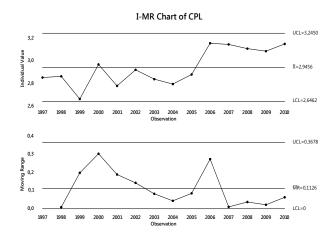

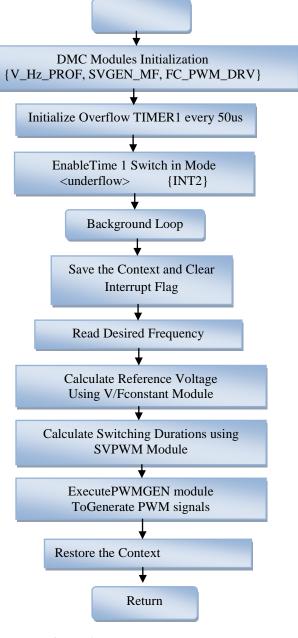

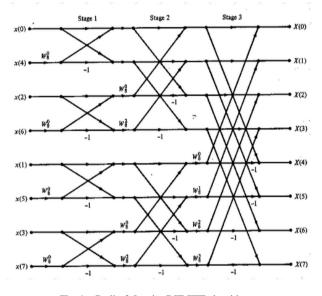

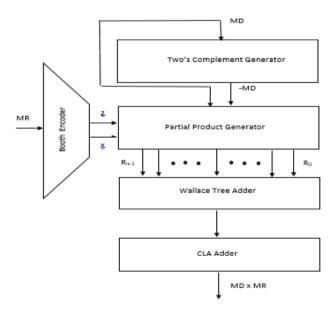

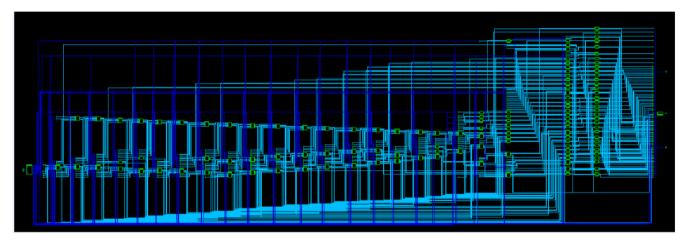

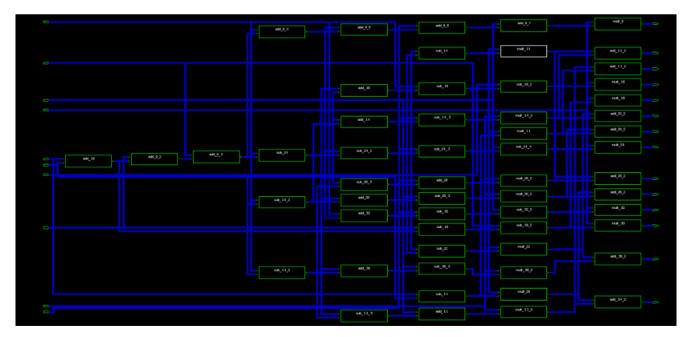

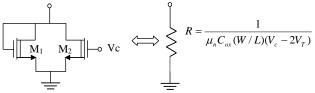

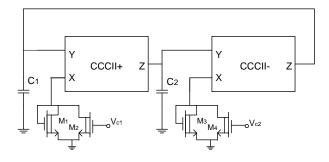

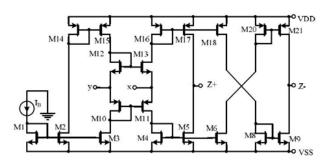

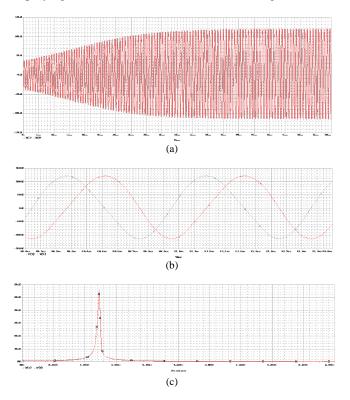

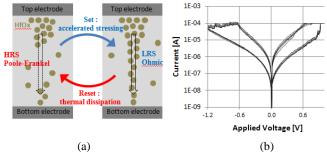

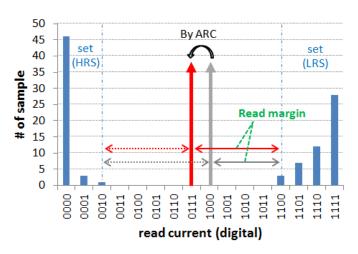

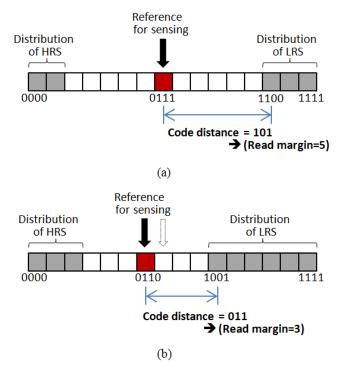

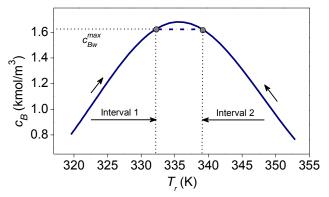

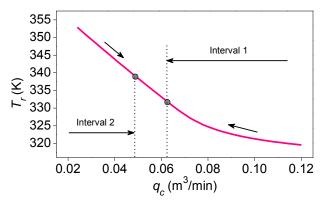

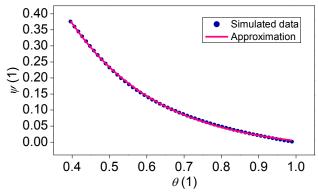

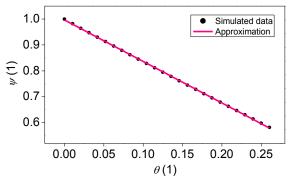

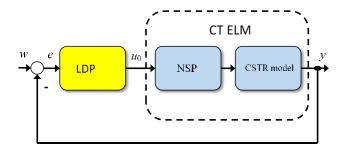

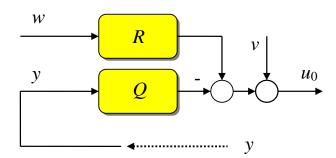

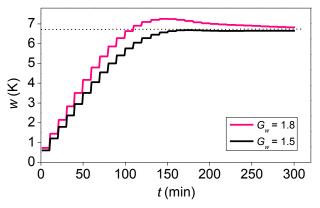

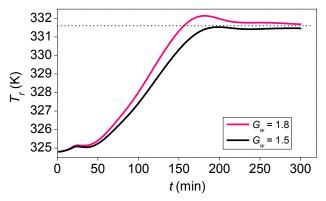

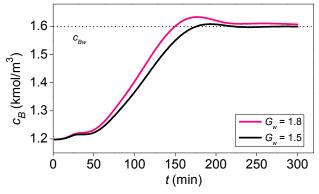

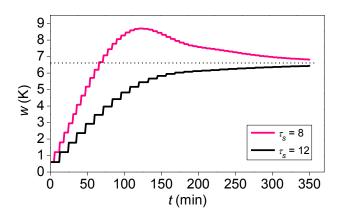

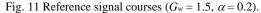

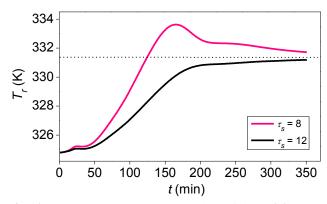

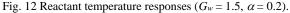

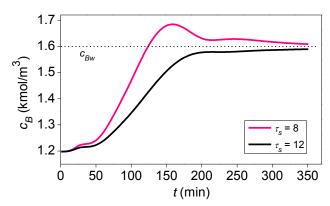

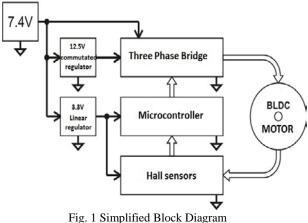

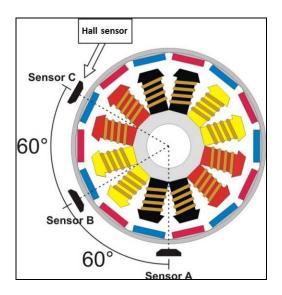

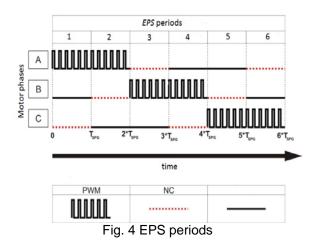

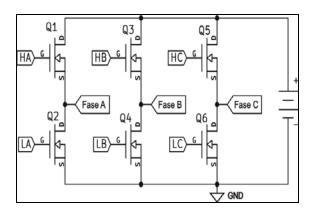

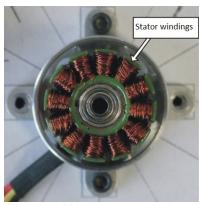

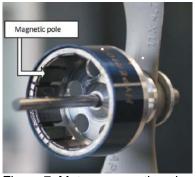

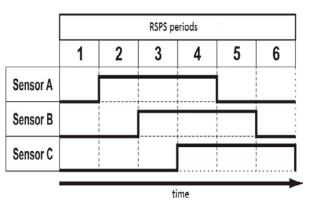

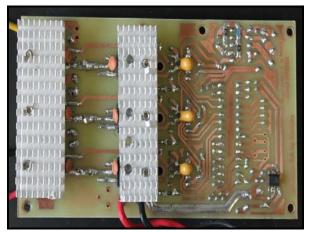

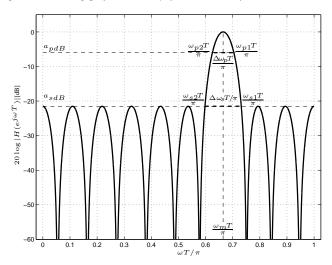

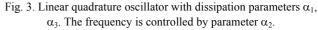

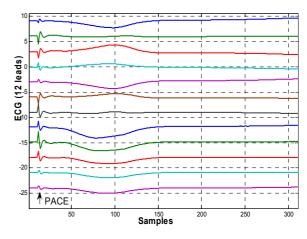

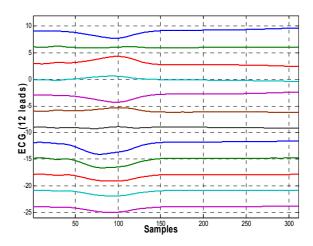

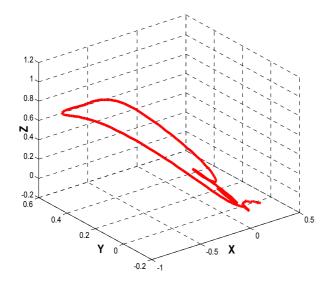

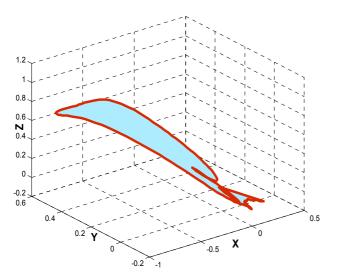

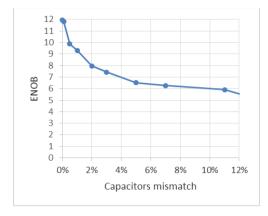

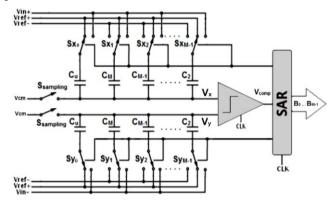

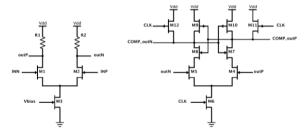

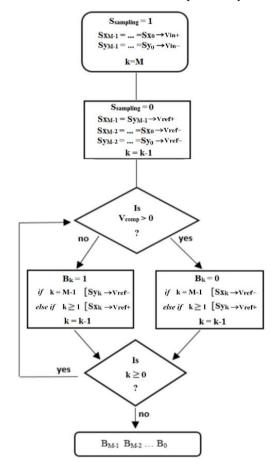

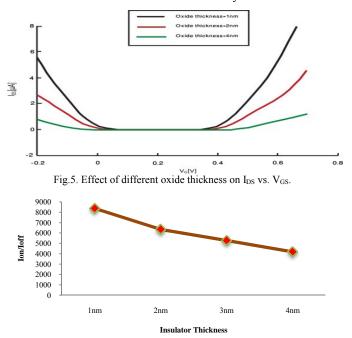

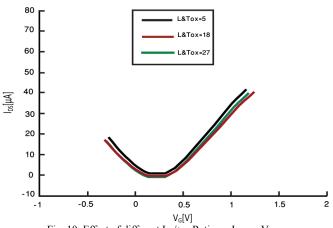

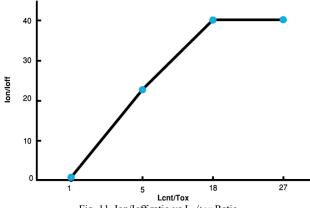

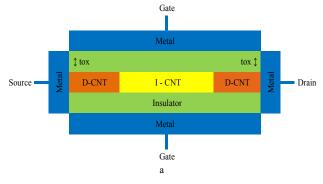

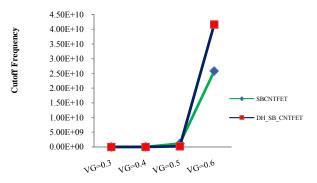

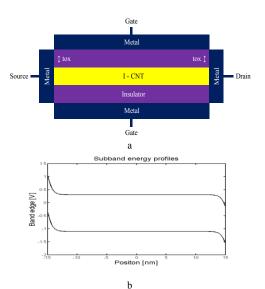

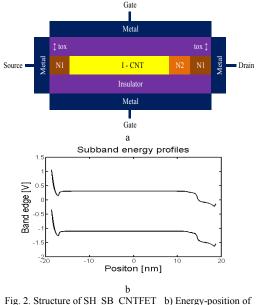

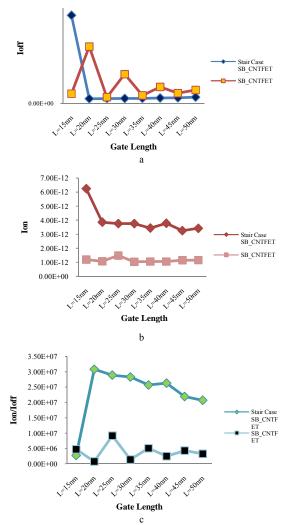

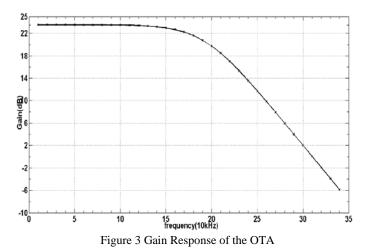

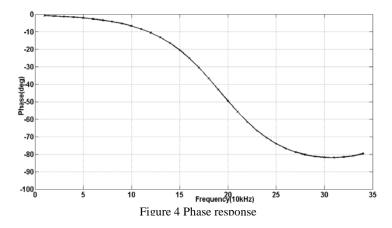

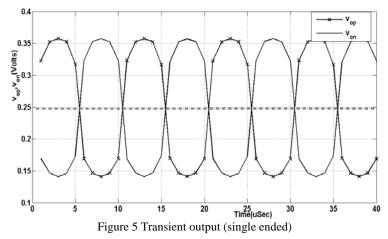

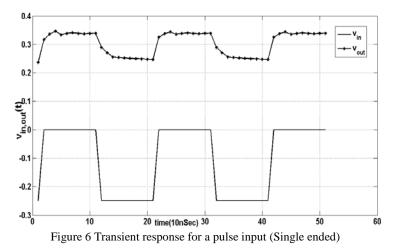

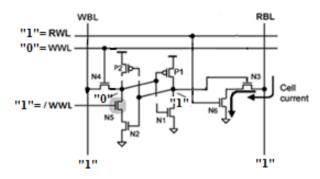

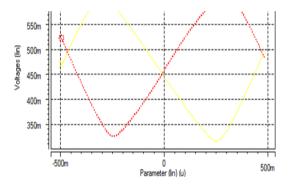

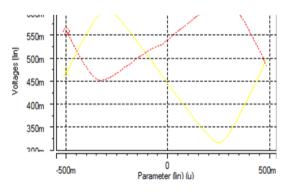

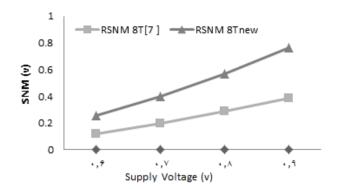

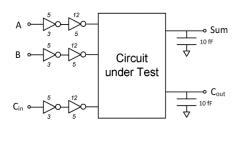

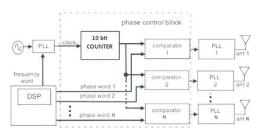

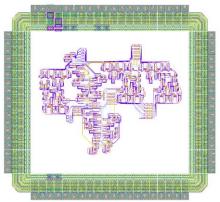

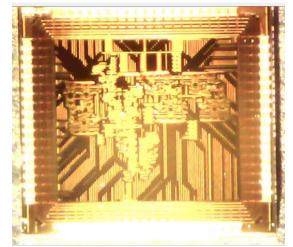

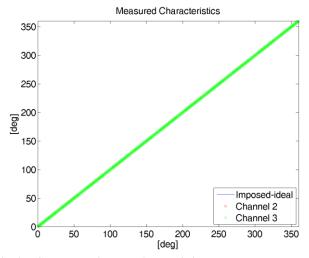

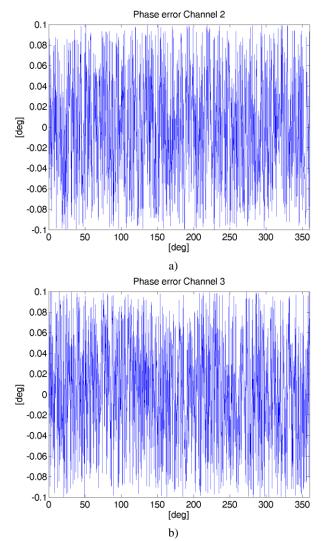

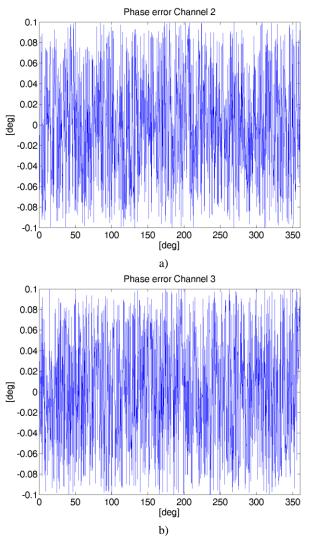

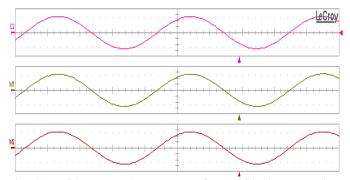

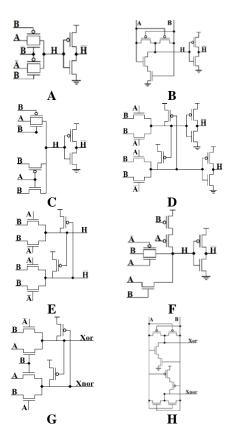

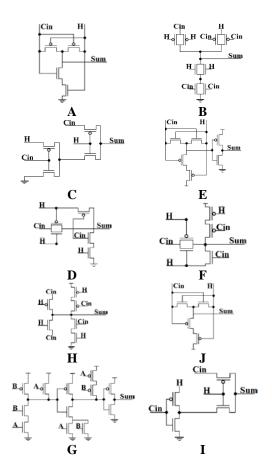

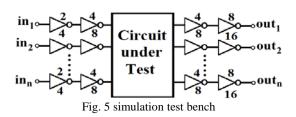

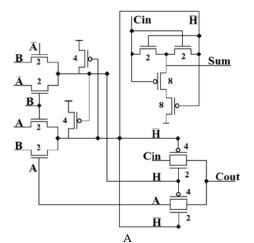

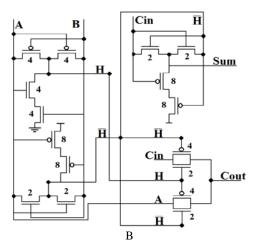

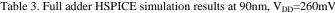

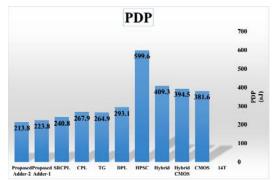

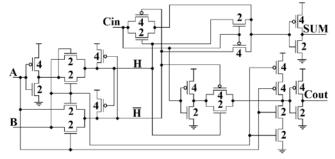

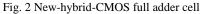

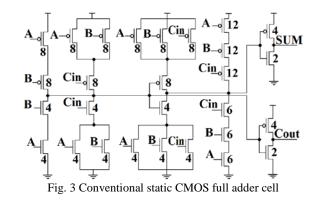

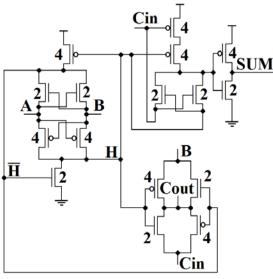

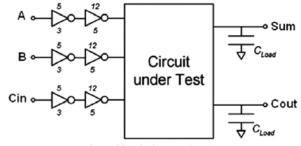

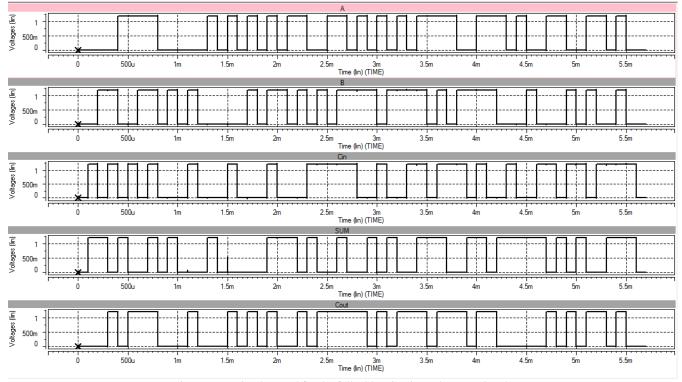

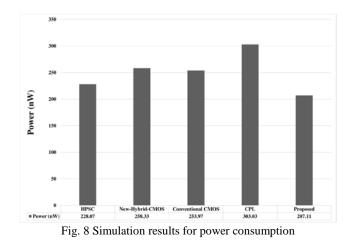

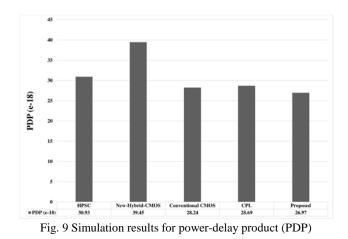

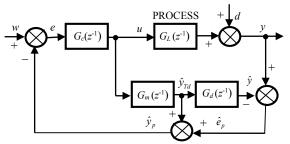

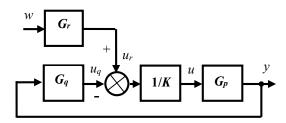

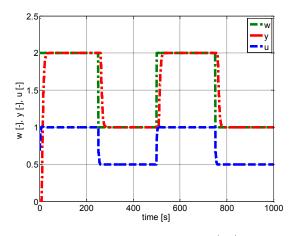

Fig. 5 Impedance of Polished Stainless Steel Electrode